International Journal of Innovative Research in Science, Engineering and Technology

Volume 3, Special Issue 3, March 2014

2014 International Conference on Innovations in Engineering and Technology (ICIET'14) On 21<sup>st</sup> & 22<sup>nd</sup> March Organized by

K.L.N. College of Engineering, Madurai, Tamil Nadu, India

# A Novel SB-MOSFET with Record Switching Characteristic

Om Prakash Mahto<sup>#1</sup>,S. Baishya<sup>#2</sup>,Koushik Guha<sup>#3</sup>,Ajay Parmar<sup>#4</sup>

Department of Electronics and Communication, National Institute of Technology Silchar, Assam, India.

**ABSTRACT**—This paper presents a novel 65 nm nchannel SB-MOSFET(Schottky barrier MOSFET) based Tunnel Field Effect transistor using Non-Local Band-to-Band tunneling model that shows the good switching characteristic.Stacks of Erbium silicide and Cobalt silicide is used as source/drain because of low schottky barrier height of Erbium silicide and high schottky barrier height of Cobalt silicide. TCAD Simulation is made which shows the result with the record high  $I_{on}/I_{off}$  ratio of  $4.08 \times 10^9$  and the steepest pointsub threshold swing of 77.12mV/decade.

**KEYWORDS**—SB-MOSFET; rare earth(RE) metals; silicide source/drain; High-K materials; Sub threshold Swing; Band-to-Band Tunneling Model.

# I. INTRODUCTION

Recently MOSFET with Schottky source and drain hasbeen considered an important candidate for VLSI because of its ultra-shallow junctions to minimize shortchannel effects, low source and drain series resistances, simplified processes, and the elimination of minority carrier injection into the substrate[1].Schottky Barrier MOSFETs(SB-MOSFETs)can be used as an alternative to conventional MOSFETs.SB-MOSFETshave their source/drain regions replaced with metal, typically silicide,Nickel Titanium silicides such as silicide, Platinum silicide, Erbium silicide etc. as opposed to highly doped silicon regions in conventional devices .The main advantage are low parasitic ,superior scaling properties ease of fabrication and low thermal budget.SB-MOSFETs have also been shown to offer immunity to latch-up by essentially eliminating parasitic bipolar actions.An excellent scalability of SB-MOSFETs to sub-10nm gate lengths is feasible due to the low resistance of the silicide regions and atomically abrupt silicide/silicon junctions. silicides are typically at temperature below 973.15 kelvin which makes them compatible for integration with high-K dielectrics and metal gate stacks used in a conventionally sub-65nm CMOS process flow [1]-[5].

# II. STRUCTURE & PHYSICS OF THE DEVICE

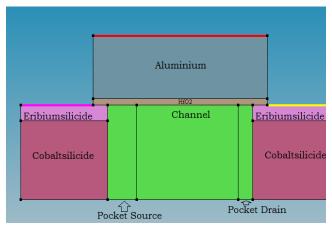

Fig.1 shows SB-MOSFET with gate length of 65 nm with supply voltage of 0.5 Vand metal as gate material. The source & channel regions are of p-type and drain and gate regions are of n-type material.In all the simulations, pocket source doped with a concentration of  $1 \times 10^{21}$  (n type atoms/cm<sup>3</sup>), channel is doped with concentration of  $1 \times 10^{20}$  (p type atoms/cm<sup>3</sup>) and pocket drain doped with a concentration of  $1 \times 10^{21}$  (n type atoms/cm<sup>3</sup>). A high-k material HfO<sub>2</sub> which is used as the dielectric and Aluminum gate are placed over the channelwith work function of 4.03 eV. Leakage current through the gate oxide should be minimum for the desired reliability and this will achieve when the gate oxide resist with the high electric field. Here, stacks of silicides is used as source/drain in which top material(i.e, Erbium silicide) possess low barrier height(0.28ev) is to provide high on-state current and bottom material(i.e,Cobaltsilicide) possess high barrier height is to provide low off-state current [5]. Non-localBand-to-Band Tunneling model is used which presents the nonlocal generation rate of electrons and holes caused by phonon-assisted Band-to-Band Tunneling as available in TCAD Synopsys[9],[13].

Let's start the mechanism of SB-MOSFETs from schottky contacts , as we know that for n-type semiconductor with  $\Phi_M > \Phi_s$ ,its equation of current(thermionic emission current , J) in which electron is flowing from metal to semiconductor is

$$\mathbf{J} = \mathbf{A}exp(-\frac{q\Phi}{kT})$$

where A is the effective Richardson's constant is the temperature, k is the Boltzmann constant, q is the charge and  $\Phi$  is the schottky barrier height. But The total current density across a Schottky barrier consists not only of the thermionic emission component but also of a field assisted (thermionic) tunneling component [3].

# M.R. Thansekhar and N. Balaji (Eds.): ICIET'14

Higher barrier height reduces thermionic emission and electron tunneling .Firstly thermionic emission takes place, as temperature is decreasing tunneling current start to takes place[13],[12].

Fig.1. Device Structure of SB-MOSFET

TABLE 1

Description about 65nm gate length SB-MOSFET

| Item             | Thickness<br>(nm) | Length<br>(nm) |

|------------------|-------------------|----------------|

| Channel          | 30                | 50             |

| Pocket Source    | 30                | 10             |

| Pocket Drain     | 30                | 5              |

| Erbiumsilicide   | 5                 | 30             |

| Cobaltsilicide   | 25                | 30             |

| Aluminium        | 20                | 75             |

| HfO <sub>2</sub> | 0.02              | 75             |

## A. TUNNELING MECHANISM

TFET is a semiconductor device in which the gate controls the source-drain current through the modulation of Band-to-Band tunneling. BTBT is the quantum mechanical phenomenon in which electrons tunnel from the valance band to condition band (or vice-versa) through the forbidden energy band gap. The important factors of BTBT models are

- a) Band structure

- b) Dimensionality of the device

- c) Local vs. Non-local.

Two different processes for BTBT are direct and phonon assisted BTBT. There are two direct tunneling models are local and non-local model. In local model, electron and holes generation profiles are the same whereas in non-local model holes are generated at the beginning and the electrons at the end of the tunneling path. To understand the nature of the BTBT it is important to understand the approximation made in various simulation models which is also useful for optimizing the design parameter of TFET. To find the optimal solution for improving the tunnel devices TCAD simulation can be an additional gadget [6, 7].

There are different models which are accepted by the device society to simulate the BTBT such as Non-local BTBT model [8, 9], Schenk BTBT model [11], Hurkx BTBT model [12], Simple (E1) BTBT model [9] etc.Schenk and Hurkx are the local models and as the name says non-local BTBT is non-local model.

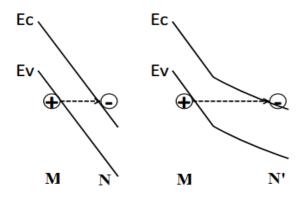

Local models means the maximum or average electric field is constant throughout the tunneling. In nonlocal models the electric field at each point in the tunneling path is dynamically changing that means the tunneling current depends on the band edge profile along the entire path between the points connected by tunneling.Fig 2 shows the 1-D view of BTBT for local and non-local tunneling model. In local model, valance electrons tunnel from position M to N, and the tunnel distance can be obtained by electric field. But in the case of non-local, valance electrons tunnel from position M to N' and the electric field is changing continuously so the tunnel distance is not found.

Fig.2.The local and non-local BTBT model.

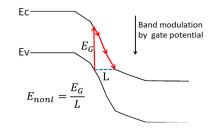

A non-local BTBT is model in which the conduction and valance band are multi-dimensionally traced to get tunnel paths. The nonlocal electric field is used in famous Kane and Keldysh's formula of BTBT generation rates. The non-local electric field  $E_{nonl}$  is defined as the average electric field along the traced tunnel path. Fig.3shows the non-local electric field using band diagram. Here, L is the tunnel length which is obtained by tracing the conduction and valance band to find the same energy level and  $E_G$  is the energy band gap [13].

Fig. 3.Non-local electric field using band diagram.

In TFETs, at the source gate overlap region band to band tunneling occurs where the electric field is strongly bended by gate, source and drain voltages. In our device, this reason is sufficient to use the non-local band to band tunneling model.

A non-local model is the non-local generation of electron and holes caused by direct or phonon assisted band-toband tunneling process. Phonon assisted band-to-band tunneling process is dominant in indirect semiconductors such as Si and Ge. The BTBT expression is given by[9]

$$R_{\text{net}}^{P} = |\nabla E_{V}(0)|C_{P}exp\left(-2\int_{0}^{x_{0}}\kappa_{V}dx\right) - 2\int_{x_{0}}^{l}\kappa_{C}dx\right) \left[\left(exp\left[\frac{\varepsilon - E_{F,n}(l)}{kT(l)}\right] + 1\right)^{-1} - \left(exp\left[\frac{\varepsilon - E_{F,p}(0)}{kT(0)}\right] + 1\right)^{-1}\right]$$

With

$$C_{P} = \int_{0}^{1} \frac{g(1+2N_{op})D_{op}^{2}}{2^{6}\pi^{2}\rho\varepsilon_{op}E_{g,tun}} \sqrt{\frac{m_{V}m_{C}}{hl\sqrt{2m_{r}E_{g,tun}}}} dx \left(\int_{0}^{x_{0}} \frac{dx}{\kappa_{V}}\right)^{-1} \left(\int_{x_{0}}^{l} \frac{dx}{\kappa_{C}}\right)^{-1} \left(\int_{x_{0}}^{l} \frac{dx}{$$

$D_{op}$ ,  $\varepsilon_{op}$  and  $N_{op} = \left[exp(\varepsilon_{op}/kT) - 1\right]^{-1}$  are deformation potential, energy and number of optical phonons respectively,  $\rho$  is the mass density and  $\kappa_V \& \kappa_C$  are the magnitudes of the imaginary wave vectors from the Keldysh dispersion relation:

$$\kappa_{V} = \frac{1}{\hbar} \sqrt{2m_{V}|\varepsilon - E_{V}|} \, \Theta(\varepsilon - E_{V})$$

$$\kappa_{C} = \frac{1}{\hbar} \sqrt{2m_{C}|E_{C} + \Delta_{C} - \varepsilon|} \, \Theta(E_{C} + \Delta_{C} - \varepsilon)$$

and  $x_0$  is the location where  $\kappa_V = \kappa_C R_{net}^P$  is the net hole recombination rate due to the phonon-assisted band-to-band tunneling process.

## III. Result & Discussions

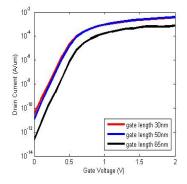

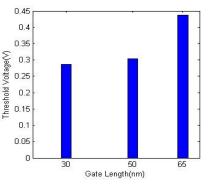

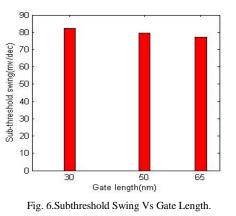

We have calculated drain current Vs gate voltage, Ion/Off ratio and sub threshold swing at different gate lengths and gate lengths Vs threshold voltage on Synopsys TCAD [10]. All results are based on simulation .Fig.4 shows the drain current versus gate voltage for three different gate Lengths.

Fig. 4.I<sub>d</sub>vs.V<sub>gs</sub> curve for different gate lengths.

Here, we can see that the gate length of 65nm shows the highest  $I_{on}/I_{off}$  ratio in comparison to other gate lengths.

| Gate<br>Length | Ion/Ioff             | Subthreshold<br>(mV/decade) |

|----------------|----------------------|-----------------------------|

| 30nm           | 7.91×10 <sup>7</sup> | 82.141                      |

| 50nm           | 3.23×10 <sup>8</sup> | 79.624                      |

| 65nm           | $4.08 \times 10^{9}$ | 77.129                      |

TABLE.2.

Ion/Off ratio and sub threshold swing at different gate lengths

Fig. 5.Gate Length Vs Threshold voltage .

With increase in gate length ,threshold voltage also increase because of DIBL(Drain induced barrier lowering ) as shown in Fig.5. One of the important requirements regarding switching characteristic of the Tunnel FET is the subthreshold swing.Fig.Fig.6 shows the pointsub threshold swing (SS) decreases with increase in gate length and it show good result at 65nm gate length.

### IV. CONCLUSION

This work presents a novel 65 nm n-channel SB-MOSFET with stack of Erbiumsilicide and Cobaltsilicide as the source/drain, Aluminium as the gate, p-type material as the substrate and HfO<sub>2</sub> dielectric constant as oxide.TCAD Simulation is made which shows the result with the record high  $I_{on}/I_{off}$  ratio of  $4.08 \times 10^9$  and the sub threshold swing of 77.12 mV/decade. This is the highest  $I_{on}/I_{off}$  ratio recorded for the SB-MOSFET.

## ACKNOWLEDGMENT

Theauthors acknowledge that the work was supported by the All India Council for Technical Education (AICTE), under Grant 8023/BOR/RID/RPS-253/2008-09.

#### References

M.P. Lepselter and S.M. Sze, Proc. IEEE 56, 1088 ,1968.

[1]

[2] Li Ding-Yu Wang Yi Sun Lei, Zhang Sheng-Dong, Liu Xiao-Yan and Han Ru-Qi, "Schottky barrier MOSFET structure with silicide source/drain on buried metal" *Chin. Phys. Soc. and IOP Publishing Ltd*, Vol 16, No1, January 2007 1009-1963/2007/16(01)/0240-05 c 2007.

[3] Padovani, F.A. and R. Stratton, Field and thermionic-field emission in Schottky barriers. *Solid-State Electronics*, 9(7): p. 695-

emission in Schottky barriers.*Solid-State Electronics*, 9(7): p. 695-707.1966.

[4] Ajayan.*Jet al* "study of effects High-k Dielectrics in schottky

Tunneling source MOSFETs " 978-1-4673-5090-7113/\$31.00©2013 IEEE,2013.

[5] Moongyu Jang*et al* "A 50-nm-gate-length erbium-silicided n-type schottky barrier metal-oxide-semiconductor field effect transistor"*Applied physics letters*, Volume 84, Number 5.

[6] K. Boucart, A. Ionescu, and W. Riess, "A simulation-based study of sensitivity to parameter fluctuations of silicon tunnel FETs," in *ESSDERC, IEEE*, pp. 345–348,2010.

[7] C. Hu, P. Patel, A. Bowonder, K. Jeon, S. H. Kim, W. Y. Loh, C. Y. Kang, J. Oh, P. Majhi, A. Javey, T.-J. K. Liu, and R. Jammy, "Prospect of tunneling green transistor for 0.1V CMOS," in *IEDM*, *IEEE*, pp. 16.1.1–16.1.4,2010.

[8] PierpaoloPalestri," Semiclassical and quantum mechanical modeling of tunnel FEt devices",*EPFL*,2012.

[9] M. Ieong, P. Solomon, S. Laux, H.-S. Wong, and D. Chidambarrao, "Comparison of raised and Schottky source/drain MOSFETs using a novel tunneling contact model," in *IEDM*, *IEEE*, pp. 733–736, 1998.

[10] Sentaurus TCAD, Release E-2010.12 Ed., *Synopsys, Mountain View*, CA, USA, 2010.

[11] A. Schenk, "Rigorous theory and simplified model of the band-to-band tunneling in silicon," *Solid-State Electronics*, vol. 36, no. 1, pp. 19–34, 1993.

[12] G. Hurkx, D. Klaassen, and M. Knuvers, "A new recombination model for device simulation including tunneling," *IEEE Transactions on Electron Devices*, vol. 39, no. 2, pp. 331–338,1992.

[13] Jhaveri, R. and J. Woo. "Schottky Tunneling Source MOSFET Design for Mixed Mode and Analog Applications". in *Solid-State Device Research Conference*,

2006. ESSDERC 2006. Proceeding of the 36th European. 2006.

[14] John M. Larson and John P. Snyder "Overview and Status of Metal S/D Schottky-Barrier MOSFET Technology"*IEEE TransactionOnElectronDevices*, VOL. 53, NO. 5, MAY 2006.