## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 8, August 2013

# A Novel Simplified Single-Phase Cascaded Multistring and H-bridge Multilevel Inverter

K. Lakshmi Ganesh<sup>1</sup>, M.Balaji<sup>2</sup>, K. Durga prakash<sup>3</sup>

Assistant professor, Dept. of EEE, Vishnu Institute of Technology, W.G.Dist, Andhra Pradesh, India <sup>1</sup>

Assistant professor, Dept. of EEE, Vishnu Institute of Technology, W.G.Dist, Andhra Pradesh, India <sup>2</sup>

Assistant professor, Dept. of EEE, Vishnu Institute of Technology, W.G.Dist, Andhra Pradesh, India 3

**Abstract**: This paper presents a novel simplified single-phase cascaded Multistring and H-bridge Multilevel inverter. This multilevel inverter produces higher voltage levels which includes nine, eleven, thirteen and fifteen levels operates with 10 switches from three voltage sources. In this configuration all switches operates with fundamental frequency with low switching losses. This multilevel inverter produces higher output voltage levels near to sine wave with less harmonic content. Corresponding increment in number of levels in this multilevel inverter, there is a good considerable decrement in harmonic content. The simulation results are shown in the Matlab/simulink 2009b.

**Keywords**: Multilevel Inverters, Sinusoidal phase shift carrier PWM, level shift Phase Dispose PWM, Pulse generation, THD analysis.

#### I. INTRODUCTION

Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel converter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind and fuel cells can be easily interfaced to a multilevel converter system for a high power application [1-3].

The concept of multilevel converters has been introduced since 1975[4]. The term multilevel began with the three level converters [5]. Subsequently, several multilevel converter topologies have been developed [6-13]. However, the elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a stair case voltage waveform. Capacitors, batteries and renewable voltage sources can be used as the multiple dc voltage sources.

The cascaded H-bridge five-level multilevel inverter (MLI) has 8 switches. Sinusoidal phase shift carrier PWM used for Cascaded H-ridge five-level MLI, all the switches operated with carrier switching frequency, so the switching losses are high. The same five-level output voltage produced with 6 switches (Multistring five-level MLI), the level shift phase dispose PWM used. In these inverter, the 2 switches operated with fundamental frequency and remaining switches operated with carrier switching frequency, then switching losses are low compared with the Cascaded H-bridge five-level MLI [14].

The PWM techniques used in the MLIs, the switching losses are high and efficiency decreases and the switches capable of carrier switching frequency, the cost of switches are high.

In this paper the switches operated with fundamental switching frequency, which the switching losses are decreases and efficiency increases. The switches capable of fundamental switching frequency and then cost of switches are low. A Proposed novel simplified cascaded multistring and H-bridge MLI have 10 switches and three batteries. The proposed

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

novel simplified cascaded multistring and H-bridge MLI produced nine, eleven, thirteen and fifteen level stair case output voltage with only 10 switches. The output voltage level increases corresponding THD decreases.

The basic Inverter converts DC into AC at desired output voltage and frequency. The inverter output produces two voltage levels  $+V_{dc}$  and  $-V_{dc}$ . The inverter output produces symmetrical square wave. The square wave output voltage contains infinite number of odd harmonics. The harmonics reduced by using Multilevel Inverters. Multilevel inverter is defined as level refers to the various voltage values in a cycle. The Multilevel inverter starting from three level output voltage. The basic inverter produces three voltage levels 0,  $+V_{dc}$  and  $-V_{dc}$ . The three level output voltage contains the harmonic content reduced compared to the two level output voltage. The voltage levels are increasing, the harmonic content in the output voltage reduces and the easily sine wave output wave form produces from multilevel inverters.

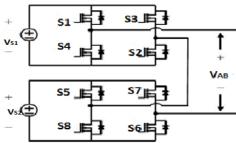

#### A. Cascaded H-bridge Five-level Multilevel Inverter (MLI)

The One full H-bridge inverter produces three voltage levels. They are 0,  $+V_{dc}$  and  $-V_{dc}$ . The five-level output voltage are producing from two full H-bridge inverters connected in cascaded form. They are 0,  $+2V_s$ ,  $+V_s$ ,  $-2V_s$  and  $-V_s$ . The sinusoidal phase shift carrier pulse width modulation used for cascaded H-bridge five-level inverter. The carrier frequency used for carrier wave 1860Hz.

Fig. 1 Cascaded H-bridge 5-level MLI

TABLE I SWITCHING SEQUENCE OF EIGHT SWITCHES

| Output  | Sv | Switches in Cascaded H-bridge Five level |           |           |    |           |           |           |  |

|---------|----|------------------------------------------|-----------|-----------|----|-----------|-----------|-----------|--|

| Voltage |    |                                          |           | M         | LI |           |           |           |  |

|         | S1 | <b>S2</b>                                | <b>S3</b> | <b>S4</b> | S5 | <b>S6</b> | <b>S7</b> | <b>S8</b> |  |

| +2Vs    | 1  | 1                                        | 0         | 0         | 1  | 1         | 0         | 0         |  |

| +Vs     | 1  | 1                                        | 0         | 0         | 1  | 0         | 1         | 0         |  |

| +Vs     | 1  | 0                                        | 1         | 0         | 1  | 1         | 0         | 0         |  |

| 0       | 1  | 0                                        | 1         | 0         | 1  | 0         | 1         | 0         |  |

| 0       | 1  | 0                                        | 1         | 0         | 0  | 1         | 0         | 1         |  |

| 0       | 0  | 1                                        | 0         | 1         | 1  | 0         | 1         | 0         |  |

| 0       | 0  | 1                                        | 0         | 1         | 0  | 1         | 0         | 1         |  |

| -Vs     | 0  | 0                                        | 1         | 1         | 1  | 0         | 1         | 0         |  |

| -Vs     | 1  | 0                                        | 1         | 0         | 0  | 0         | 1         | 1         |  |

| -2Vs    | 0  | 0                                        | 1         | 1         | 0  | 0         | 1         | 1         |  |

In the Table I shows, '1' means switch is ON and '0' means switch is OFF in the Cascaded H-bridge 5-level MLI. The  $V_{S1}=V_{S2}=100V$  as the input voltage of inverter. The sinusoidal phase shift carrier PWM applied to the circuit, which PWM contains one reference waveform and four carrier wave forms. The phase shift of the carrier wave form is  $360^{0}/(n-1)$ , the 'n' means number of voltage levels. The first carrier wave form operated with 0 degrees, the second carrier wave form shifted with 90degrees, third carrier waveform shifted with 180degress and fourth carrier waveform shifted with 270 degrees. All switches operated with carrier switching frequency, whose switching losses are high in the above circuit. The five level output voltage produced in the above circuit.

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

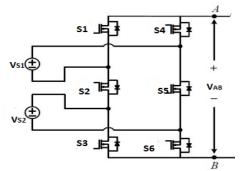

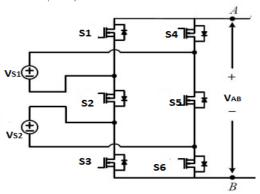

#### B. Multistring Five-level multilevel inverter (MLI) with six switches

The five-level output voltage produced by using two sources with six switches. They are 0,  $+V_{dc}$ ,  $-V_{dc}$ ,  $+2V_{dc}$  and  $-2V_{dc}$ . The level shift phase dispose pulse width modulation used in the Multistring five-level multilevel inverter with six switches, which compared to the Cascaded H-bridge Five-level Multilevel inverter then switching devices, circuit complexity, area required and also cost reduced. The  $V_{S1}$ =  $V_{S2}$ = 100V as the input voltage of this inverter. The carrier switching frequency 1860Hz used in the Multistring Five-level MLI for S1, S4, S3 and s6. The fundamental switching frequency used for S2, S5 switches.

Fig. 2 Multistring five-level MLI diagram

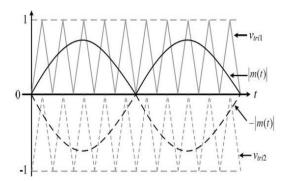

Fig.3 Modulation strategy of carrier/reference signals

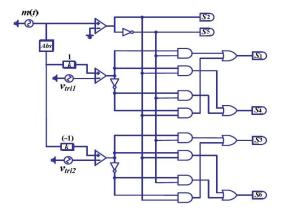

Fig. 4 Modulation logic of Multistring 5- level MLI diagram

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 8, August 2013

TABLE II SWITCHING SEQUENCE OF SIX SWITCHES

| Output<br>voltage | Multi string five-level multilevel inverter with six switches |    |    |    |    |           |  |

|-------------------|---------------------------------------------------------------|----|----|----|----|-----------|--|

| VAB               | S1                                                            | S2 | S3 | S4 | S5 | <b>S6</b> |  |

| +2Vs              | 0                                                             | 1  | 0  | 1  | 0  | 1         |  |

| +Vs               | 0                                                             | 1  | 1  | 1  | 0  | 0         |  |

| +Vs               | 1                                                             | 1  | 0  | 0  | 0  | 1         |  |

| 10                | 1                                                             | 1  | 1  | 0  | 0  | 0         |  |

| 0                 | 0                                                             | 0  | 0  | 1  | 1  | 1         |  |

| -Vs               | 1                                                             | 0  | 0  | 0  | 1  | 1         |  |

| -Vs               | 0                                                             | 0  | 1  | 1  | 1  | 0         |  |

| -2Vs              | 1                                                             | 0  | 1  | 0  | 1  | 0         |  |

In the table II shows '1' means switch is 'ON' and '0' means switch is 'OFF' in the Multistring five-level MLI diagram. In the above Fig.2 shown operated with level shift phase dispose PWM, which PWM contains two reference wave forms and two carrier waveforms in the Fig.3 shown and modulation logic of Multistring 5-level MLI in the Fig 4 shown. The above Fig.4 shown the middle switches operated with fundamental switching frequency (S2, S5) and remaining four switches operated with switching carrier frequency (S1, S3, S4, S6) of modulation logic applied to the multistring 5-level MLI (Fig.2 shown) compared to 5-level cascaded H-bridge MLI have one reference wave form and four carrier wave forms then switching losses are high in the cascaded H-bridge 5-level MLI.

The switching losses decreases in the multistring 5-level MLI compared to the Cascaded H-bridge 5-level MLI.

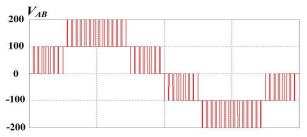

Fig. 5 Five-level Multistring Multilevel inverter five level output phase voltage of simulation waveform  $V_{AB}$

The above Fig.5 is shown 5-level output voltage of 5-level multistring MLI. The same output voltage of 5-level cascaded H-bridge MLI.

TABLE III COMPARE BETWEEN THE CASCADED H-BRIDGE MLI AND MULTISTRING MLI

| Contents             | Cascaded H-bridge     | Multistring MLI        |

|----------------------|-----------------------|------------------------|

|                      | MLI                   |                        |

| Output voltage level | Five-level            | Five-level             |

| Number of switches   | 8                     | 6                      |

| Pulse Width          | Sinusoidal Phase      | Phase dispose PWM      |

| Modulation           | shift carrier PWM     | used                   |

| technique            | used                  |                        |

| Carrier switching    | All switches          | S2,S5operated with     |

| frequency            | operated with carrier | fundamental switching  |

|                      | switching frequency   | frequency, S1,S4,S3,S6 |

|                      |                       | Operated with carrier  |

|                      |                       | switching frequency    |

| Switching losses     | High                  | low                    |

| Cost                 | High                  | low                    |

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

The above table III shows comparison between the Cascaded H-bridge MLI and Multistring MLI. The PWM techniques used for MLIs, the switching losses are high. The cost is high because PWM techniques used in the MLI (the switches capable of carrier switching frequency, so the cost of switches are high).

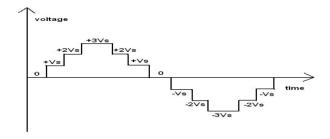

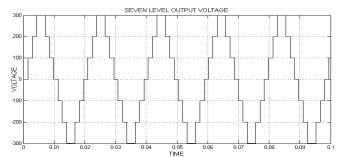

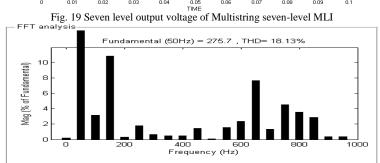

The seven level output voltage produced with same number of (six) switches of Multistring MLI. As the switches operated with fundamental switching frequency, the cost of switches is low. So, the switching losses are low and reduce the number of switches (compared to cascaded H-bridge configuration of 12 switches require to produce seven level), complexity and control circuit. The Multistring seven level MLI operation is shown below.

C. Multistring seven-level multilevel inverter (MLI) with six switches

Fig. 6 Multistring 7-level inverter MLI with 6 switches

TABLE IV 7-LEVEL SWITCHING SEQUENCE OF 6 SWITCHES

| S1 | S2 | S3 | S4 | S5 | <b>S6</b> | VAB  |

|----|----|----|----|----|-----------|------|

| 0  | 1  | 0  | 1  | 0  | 1         | +3Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | +2Vs |

| 0  | 1  | 1  | 1  | 0  | 0         | +Vs  |

| 1  | 1  | 1  | 0  | 0  | 0         | 0    |

| 0  | 0  | 0  | 1  | 1  | 1         | 0    |

| 1  | 0  | 0  | 0  | 1  | 1         | -Vs  |

| 0  | 0  | 1  | 1  | 1  | 0         | -2Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | -3Vs |

In the above Fig.6 shown, 7-level output voltage produced from multistring 7-level MLI with six switches. Generally the cascaded H-bridge configuration the 7-level output voltage is produced by using 12 switches. But the seven level output voltage produced by using six switches. In the table IV shows the switching sequence '1' means switch is 'ON' and '0' means switch is 'OFF' in the 7-level inverter with 6 switches (above Fig 6 shown). The six switches operated with fundamental switching frequency. The switching losses decreases compared to the above two MLIs.

Fig. 7 7-level output voltage of Multistring 7-level MLI with six switches

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

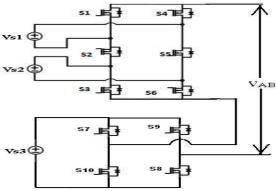

# III. PROPOSING SYSTEM OF A NOVEL SIMPLIFIED CASCADED MULTISTRING AND H-BRIDGE MULTILEVEL INVERTER

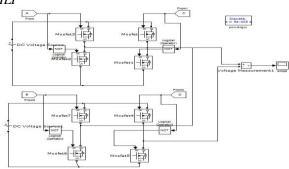

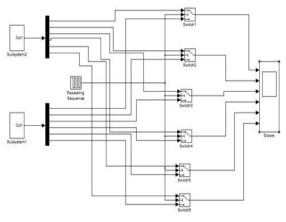

Fig. 8 Proposing system of a Novel cascaded multistring and H-bridge multilevel inverter diagram

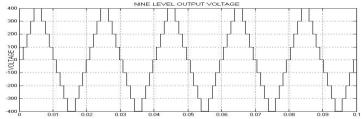

In the above circuit Fig.8 has shown three batteries and ten switches. In this circuit, all switches operated with fundamental switching frequency. A novel simplified cascaded multistring and H-bridge multilevel inverter produces nine, eleven, thirteen and fifteen level output voltage levels. In cascaded H-bridge MLI configuration nine, eleven, thirteen and fifteen level output voltage corresponding switches are 16, 20, 24 and 28 switches. So, nine, eleven, thirteen and fifteen level output voltage levels produced from only ten switches. The novel simplified cascaded multistring and H-bridge MLI operated by pulse generation of nine, eleven, thirteen, fifteen level output voltage. So switching losses decreases and reduces the cost, number of switches, area required, complexity, protection circuit and driving circuit and finally the THD reduces corresponding voltage levels increases and also the switches operated with fundamental switching frequency (pulse generation).

### A. Nine Level cascaded multistring and H-bridge MLI

In the above circuit shown (Fig.8), the input voltage V1=100V, V2=200V and V3=100V taken. The output voltage levels are  $+4V_S$ ,  $+3V_S$ ,  $+2V_S$ ,  $+V_S$ , 0,  $-V_S$ ,  $-2V_S$ ,  $-3V_S$ ,  $-4V_S$ . The nine level output voltage produced in the cascaded multistring and H-bridge multilevel inverter is called as Nine level cascaded multistring and H-bridge MLI. The all switches operated with fundamental frequency. Generally, the nine level output voltage produce with 16 switches in cascaded form but we obtained nine level output voltage by only ten switches. The nine level output voltage with switching sequence of 10 switches table V shows below. In the table '1' means switch is 'ON' and '0'means switch is 'OFF'.

TABLE V NINE LEVEL OUTPUT VOLTAGES WITH SWITCHING SEQUENCE OF 10 SWITCHES

| S1 | S2 | S3 | S4 | S5 | <b>S6</b> | S7 | S8 | S9 | S10 | VAB  |

|----|----|----|----|----|-----------|----|----|----|-----|------|

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 1  | 0  | 0   | +4Vs |

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 0  | 1  | 0   | +3Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | 1  | 0  | 1  | 0   | +2Vs |

| 0  | 1  | 1  | 1  | 0  | 0         | 1  | 0  | 1  | 0   | + Vs |

| 1  | 1  | 1  | 0  | 0  | 0         | 1  | 0  | 1  | 0   | 0    |

| 1  | 0  | 0  | 0  | 1  | 1         | 1  | 0  | 1  | 0   | - Vs |

| 0  | 0  | 1  | 1  | 1  | 0         | 1  | 0  | 1  | 0   | -2Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 1  | 0  | 1  | 0   | -3Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 0  | 0  | 1  | 1   | -4Vs |

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

#### B. Eleven Level cascaded multistring and H-bridge MLI

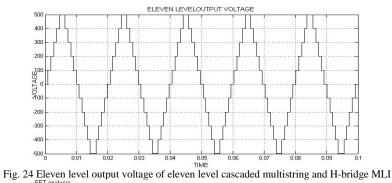

In the above circuit shown (Fig.8), the input voltage V1=100V, V2=200V and V3=200V taken. The output voltage levels are  $+5V_S$ ,  $+4V_S$ ,  $+3V_S$ ,  $+2V_S$ ,  $+V_S$ ,  $0,-V_S$ ,  $-2V_S$ ,  $-3V_S$ ,  $-4V_S$ ,  $-5V_S$ . The eleven level output voltage produced in the cascaded multistring and H-bridge MLI is called as Eleven level cascaded multistring and H-bridge MLI. The all switches operated with fundamental switching frequency. Generally, the eleven level output voltage produce by 20 switches in cascaded form but we obtained eleven level output voltage with only ten switches. The eleven level output voltage with switching sequence 10 switches table VI shown below. In the table '1' means switch is 'ON' and '0' means switch is 'OFF'.

TABLE VI ELEVEN LEVEL OUTPUT VOLTAGES WITH SWITCHING SEQUENCE OF 10 SWITCHES

| S1 | S2 | S3 | S4 | S5 | <b>S6</b> | S7 | S8 | S9 | S10 | VAB  |

|----|----|----|----|----|-----------|----|----|----|-----|------|

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 1  | 0  | 0   | +6Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | 1  | 1  | 0  | 0   | +5Vs |

| 0  | 1  | 1  | 1  | 0  | 0         | 1  | 1  | 0  | 0   | +4Vs |

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 0  | 1  | 0   | +3Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | 1  | 0  | 1  | 0   | +2Vs |

| 0  | 1  | 1  | 1  | 0  | 0         | 1  | 0  | 1  | 0   | + Vs |

| 1  | 1  | 1  | 0  | 0  | 0         | 1  | 0  | 1  | 0   | 0    |

| 1  | 0  | 0  | 0  | 1  | 1         | 1  | 0  | 1  | 0   | - Vs |

| 0  | 0  | 1  | 1  | 1  | 0         | 1  | 0  | 1  | 0   | -2Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 1  | 0  | 1  | 0   | -3Vs |

| 1  | 0  | 0  | 0  | 1  | 1         | 0  | 0  | 1  | 1   | -4Vs |

| 0  | 0  | 1  | 1  | 1  | 0         | 0  | 0  | 1  | 1   | -5Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 0  | 0  | 1  | 1   | -6Vs |

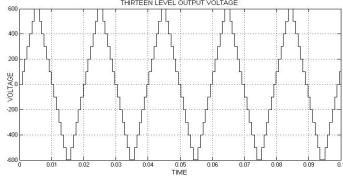

### C. Thirteen Level cascaded multistring and H-bridge MLI

In the above circuit shown (Fig.8), the input voltage V1=100V, V2=200V and V3=300V taken. The output voltage levels are  $+6V_S$ ,  $+5V_S$ ,  $+4V_S$ ,  $+3V_S$ ,  $+2V_S$ ,  $+V_S$ , 0,  $-V_S$ ,  $-2V_S$ ,  $-3V_S$ ,  $-4V_S$ ,  $-5V_S$ ,  $-6V_S$ . The thirteen level output voltage produced in the cascaded multistring and H-bridge MLI is called as Thirteen level cascaded multistring and H-bridge MLI. The all switches operated with fundamental switching frequency. Generally, the thirteen level output voltage produce with 24 switches in cascaded form but we obtained thirteen level output voltage by only ten switches. The thirteen level output voltage with switching sequence 10 switches table 7 shown below. In table '1' means switch is 'ON' and '0' means switch is 'OFF'.

TABLE VII THIRTEEN LEVEL OUTPUT VOLTAGES WITH SWITCHING SEQUENCE OF 10 SWITCHES

| S1 | S2 | S3 | S4 | S5 | <b>S6</b> | S7 | S8 | S9 | S10 | VAB  |

|----|----|----|----|----|-----------|----|----|----|-----|------|

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 1  | 0  | 0   | +5Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | 1  | 1  | 0  | 0   | +4Vs |

| 0  | 1  | 0  | 1  | 0  | 1         | 1  | 0  | 1  | 0   | +3Vs |

| 1  | 1  | 0  | 0  | 0  | 1         | 1  | 0  | 1  | 0   | +2Vs |

| 0  | 1  | 1  | 1  | 0  | 0         | 1  | 0  | 1  | 0   | + Vs |

| 1  | 1  | 1  | 0  | 0  | 0         | 1  | 0  | 1  | 0   | 0    |

| 1  | 0  | 0  | 0  | 1  | 1         | 1  | 0  | 1  | 0   | - Vs |

| 0  | 0  | 1  | 1  | 1  | 0         | 1  | 0  | 1  | 0   | -2Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 1  | 0  | 1  | 0   | -3Vs |

| 0  | 0  | 1  | 1  | 1  | 0         | 0  | 0  | 1  | 1   | -4Vs |

| 1  | 0  | 1  | 0  | 1  | 0         | 0  | 0  | 1  | 1   | -5Vs |

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

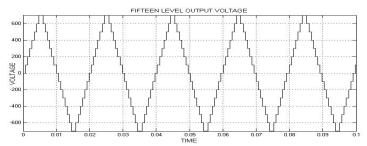

#### D. Fifteen Level cascaded multistring and H-bridge MLI

In the above circuit shown (Fig.8), the input voltage V1=100V, V2=200V and V3=400V taken. The output voltage levels are  $+7V_S$ ,  $+6V_S$ ,  $+5V_S$ ,  $+4V_S$ ,  $+3V_S$ ,  $+2V_S$ ,  $+V_S$ , 0,  $-V_S$ ,  $-2V_S$ ,  $-3V_S$ ,  $-4V_S$ ,  $-5V_S$ ,  $-6V_S$ ,  $-7V_S$ . The fifteen level output voltage produced in the cascaded multistring and H-bridge MLI is called as Fifteen level cascaded multistring and H-bridge MLI. The all switches operated with fundamental switching frequency. Generally, the fifteen level output voltage produce with 24 switches in cascaded form but we obtained fifteen level output voltage by only ten switches. The fifteen level output voltage with switching sequence 10 switches table VIII shown below. In table '1' means switch is 'ON' and '0' means switch is 'OFF'.

TABLE VIII FIFTEEN LEVEL OUTPUT VOLTAGES WITH SWITCHING SEOUENCE OF 10 SWITCHES

| S1 | S2 | S3 | S4 | <b>S5</b> | <b>S6</b> | S7 | S8 | S9 | S10 | VAB  |

|----|----|----|----|-----------|-----------|----|----|----|-----|------|

| 0  | 1  | 0  | 1  | 0         | 1         | 1  | 1  | 0  | 0   | +7Vs |

| 1  | 1  | 0  | 0  | 0         | 1         | 1  | 1  | 0  | 0   | +6Vs |

| 0  | 1  | 1  | 1  | 0         | 0         | 1  | 1  | 0  | 0   | +5Vs |

| 1  | 1  | 1  | 0  | 0         | 0         | 1  | 1  | 0  | 0   | +4Vs |

| 0  | 1  | 0  | 1  | 0         | 1         | 1  | 0  | 1  | 0   | +3Vs |

| 1  | 1  | 0  | 0  | 0         | 1         | 1  | 0  | 1  | 0   | +2Vs |

| 0  | 1  | 1  | 1  | 0         | 0         | 1  | 0  | 1  | 0   | + Vs |

| 1  | 1  | 1  | 0  | 0         | 0         | 1  | 0  | 1  | 0   | 0    |

| 1  | 0  | 0  | 0  | 1         | 1         | 1  | 0  | 1  | 0   | - Vs |

| 0  | 0  | 1  | 1  | 1         | 0         | 1  | 0  | 1  | 0   | -2Vs |

| 1  | 0  | 1  | 0  | 1         | 0         | 1  | 0  | 1  | 0   | -3Vs |

| 1  | 1  | 1  | 0  | 0         | 0         | 0  | 0  | 1  | 1   | -4Vs |

| 1  | 0  | 0  | 0  | 1         | 1         | 0  | 0  | 1  | 1   | -5Vs |

| 0  | 0  | 1  | 1  | 1         | 0         | 0  | 0  | 1  | 1   | -6Vs |

| 1  | 0  | 1  | 0  | 1         | 0         | 0  | 0  | 1  | 1   | -7Vs |

### E. Different Voltages are taken as the source voltages of the cascaded multistring and H-bridge MLI

| No of levels | No of<br>Switches | V1 | V2  | V3  | Output Voltage<br>in V |

|--------------|-------------------|----|-----|-----|------------------------|

| 9            | 10                | Vs | 2Vs | Vs  | 4Vs                    |

| 11           | 10                | Vs | 2Vs | 2Vs | 5Vs                    |

| 13           | 10                | Vs | 2Vs | 3Vs | 6Vs                    |

| 15           | 10                | Vs | 2Vs | 4Vs | 7Vs                    |

The nine, eleven, thirteen and fifteen levels output voltage got only from ten switches corresponding to respective voltage sources taken.

The above table 9 shows different voltages are taken for cascaded multistring and H-bridge MLI. The cascaded multistring and H-bridge MLI are simulated the different output voltage levels used by the table IX.

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

### IV. MATLAB/SIMULATION RESULTS

### A. Cascaded H-bridge Five-level MLI

Fig. 9 Cascaded H-bridge Five level MLI simulink diagram

The simulation diagram for cascaded H-bridge five level inverter diagram as shown above.

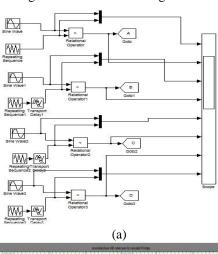

Fig. 10 (a) Sinusoidal phase shift carrier PWM simulink diagram (b) Reference and carrier waveforms of PWM generation

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

Fig. 11 Five level output voltage of Cascaded H-bridge Five-level MLI  $\,$

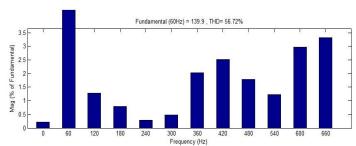

Fig. 12 THD of 5-level output voltage of Cascaded H-bridge five-level MLI

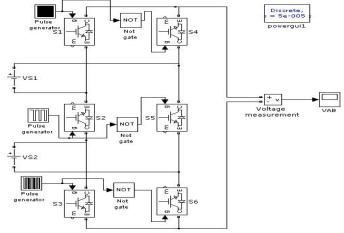

### B. Multistring Five-level MLI

Fig.13 Mulstring Five-level MLI simulink diagram

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

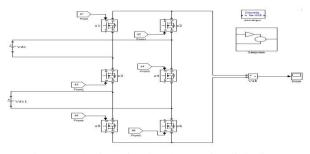

(b) Fig. 14 (a) subsystem2 of Phase disposes PWM (b) Subsystem1 of Phase disposes PWM

The above Fig 14(a) is shown subsystem2 of phase dispose PWM technique (Fig.15) and Fig.14 (b) shown subsystem1 of phase dispose PWM technique (Fig.15).

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

1940.55

194

(a)

(b)

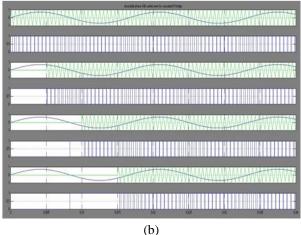

Fig. 15 (a) Phase dispose PWM technique

(b) PWM generation of six switches

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

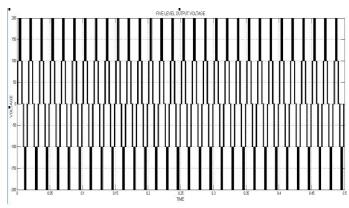

Fig. 16 Five level output voltage of Multistring Five-level MLI

Fig. 17 THD of Five level output voltage of Multistring Five-level MLI

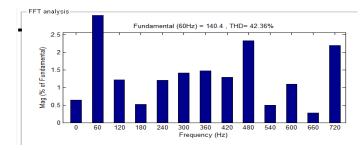

The PWM techniques used in the Cascaded H-bridge five-level MLI and Multistring Five level MLI simulated as shown above. The THD value low (42.36%) in the multistring five levels MLI compared with the Cascaded H-bridge five-level MLI (56.72%).

The switching losses are high, cost of switches high and efficiency decreases in the PWM techniques used for above two five level MLIs. The seven level output voltage produced with same number of switches (six) Multistring MLI as shown below. All the switches operated with fundamental switching frequency then switching losses decreases and efficiency increases.

### C. Multistring 7-level MLI with six switches

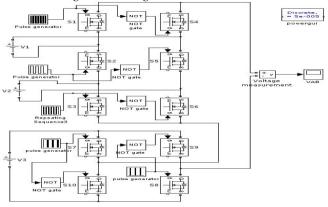

Fig.18 Multistring seven level MLI inverter with six switches simulink diagram

## International Journal of Advanced Research in Electrical, **Electronics and Instrumentation Engineering**

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

Fig. 20 THD value of 7 level output voltage seven-level multisring MLI with six switches

### D. Proposing system of cascaded multistring and H-bridge MLI

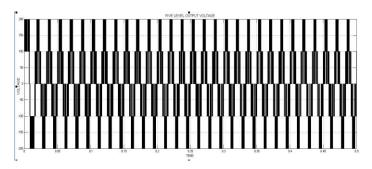

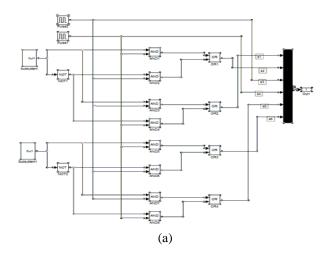

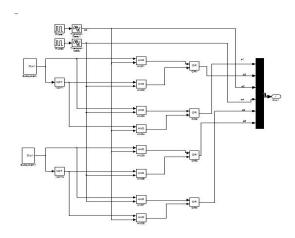

Fig. 21 nine, eleven, thirteen, fifteen level cascaded multistring and H-bridge MLI of simulink diagram

### 1) Nine level cascaded multistring and H-bridge MLI

Fig. 22 nine level output voltage of nine level cascaded multistring and H-brige MLI

## International Journal of Advanced Research in Electrical, **Electronics and Instrumentation Engineering**

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

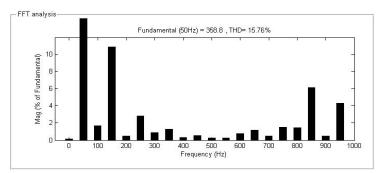

Fig. 23 THD value of nine level output voltage of nine level cascaded multistring and H-bridge MLI

#### 2) Eleven level cascaded multistring and H-bridge MLI

Fig. 25 THD value of 11 level output voltage of eleven level cascaded multistring and H-bridge MLI

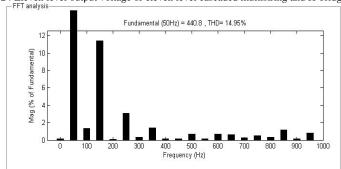

### 3) Thirteen level cascaded multistring and H-bridge MLI

Fig. 26 13- level output voltage of thirteen level cascaded multistring and H-bridge MLI

Copyright to IJAREEIE 3662 www.ijareeie.com

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 8, August 2013

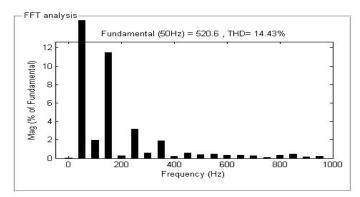

Fig. 27 THD value of 13 level output voltage of thirteen level cascaded multistring and H-bridge MLI

### 4) Fifteen level cascaded multistring and H-bridge MLI

Fig. 28 Fifteen level output voltage Fifteen level cascaded multistring and H-bridge MLI

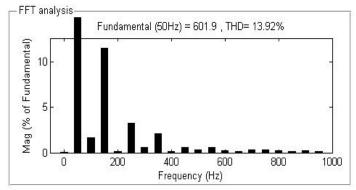

Fig. 29 THD value of 15 level output voltage of fifteen level cascaded multistring and H-bridge MLI

### TABLE X COMPARE BETWEEN CASCADED H-BRIDGE MLI AND PROPOSED CASCADED MULTISTRING AND H-BRIGE MLI

| Output            | Number of switches        |                                                         |  |  |  |  |

|-------------------|---------------------------|---------------------------------------------------------|--|--|--|--|

| Voltage<br>levels | Cascaded H-<br>bridge MLI | Proposed<br>Cascaded<br>Multistring And<br>H-Bridge MLI |  |  |  |  |

| 9 level           | 16                        | 10                                                      |  |  |  |  |

| 11level           | 20                        | 10                                                      |  |  |  |  |

| 13level           | 24                        | 10                                                      |  |  |  |  |

| 15level           | 28                        | 10                                                      |  |  |  |  |

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 8, August 2013

In the above table X shows compare between Cascaded H-bridge MLI and Proposed Cascaded Multistring And H-Bridge MLI, the switches in the cascaded form increases when increasing the output voltage levels. The cost of switches, reduce the number of switches, protection circuit, cooling equipment, control circuit increases in the cascaded form. But the Proposed Cascaded Multistring and H-Bridge MLI produced higher output voltage levels are 9, 11, 13, 15 level with ten switches only. So, the cost of switches reduce the number of switches, protection circuit, cooling equipment, control circuit decreases compared to the Cascaded H-bridge MLI.

TABLE XI THD COMPARISON OF DIFFERENT VOLTAGE LEVELS

| Proposed cascaded multistring and H-bridge multilevel inverter |    |       |  |  |  |  |  |

|----------------------------------------------------------------|----|-------|--|--|--|--|--|

| Output voltage No of IHD of output level switches voltage (%)  |    |       |  |  |  |  |  |

| 9 level                                                        | 10 | 15.76 |  |  |  |  |  |

| 11 level                                                       | 10 | 14.95 |  |  |  |  |  |

| 13 level                                                       | 10 | 14.43 |  |  |  |  |  |

| 15 level                                                       | 10 | 13.92 |  |  |  |  |  |

In the above table shows the output voltage increases corresponding to the THD value decreases in the proposed cascaded multistring and H-bridge multilevel inverter from 9 levels to 15 voltage levels.

#### V. CONCLUSION

In this paper "A Novel simplified Cascaded Multistring and H-Bridge MLI" produced higher output voltage level consisting of nine, eleven, thirteen, fifteen voltage levels. The THD value decreases, when increasing higher output voltage levels and also reduce the number of switches, cost, area required, protection circuit, cooling equipment, and driving circuit and also switching losses decreases, efficiency increases.

The Cascaded Multistring and H-Bridge MLI are easily interfaced with DERs. They are photovoltaic arrays and fuel cells.

### REFERENCES

- [1] J.Rodriguez, J.s. Lai and F.Z. Peng, "Multilevel Inverters: Survey of Topologies, Controls and Applications" IEEE Transactions on Industry Applications, vol. 49, no.4, PP.724-738, Aug. 2002.

- [2] J.S.Lai and F.Z. Peng, "Multilevel Converters-A new Breed of Power Converters", IEEE Trans. Ind Applications, vol.32.pp. 509-517, May/June 1996.

- [3] L. M. Tolbert, F.Z. Peng and T. Habetler, "Multilevel Converters for Large Electric drives", IEEE Transaction Industrial Applications, vol.35, pp. 36-44, jan/Feb.1999.

- [4] R.H. Baker and L. H. Bannister, "Electric Power Converter', U.S. Patent3 867 543, Feb. 1975.

- [5] A. Nabae, I. Takahashi and H. Akagi, "A New Neutral-point clamped PWM inverter", IEEE Trans. Ind. Applicat. Vol. IA-17, pp. 518-523, Sept/Oct. 1981.

- [6] R.H. Baker, "Bridge Converter circuit", U.S. Patent 4 270 163, May 1981.

- [7] P.W. Hammond, 'Medium voltage PWM Drive and Method", U.S. Patent 5 625 545, Apr .1977.

- [8] F.Z. Peng and J.S. Lai, "Multilevel Cascade voltage-source Inverter with DC source", U.S. Patent 5 642 275 June 24, 1997.

- [9] P.W. Hammond, "Four-quadrant AC-AC Drive and Method", U.S. Patent 6 166 513, Dec. 2000.

- [10] M. F. Aiello, P.W. Hammond and M. Rastogi, "Modular Multi-level Adjustable Supply with Series Connected Active Inputs", U.S patent 6 236 580, May 2001.

- [11] M.F.Aiello, P.W. Hammond and M. Rastogi, "Modular Multi-Level Adjustable Supply with Parallel Conneced Active Inputs", U.S.Patent 6 301 130, Oct.2001.

- [12] J.P. Lavieville, P.Carrere and T.Meynard, "Electronic ciruit for Converting Electrical Energy and a power supply Installation Making use of thereof", U.S. Patent 5 668 711 Sept. 1997.

- [13] T.Meynard, J.P. Lavieville, P.Carrere, J.Gonzalez and O. Bethoux, "Electronic circuit for converting Electrical Energy", U. S patent 5 706 188, Jan 1998.

- [14] Yi-Hung Liao, Member, IEEE and Ching-Ming Lai, Member, IEEE "Newly-Constructed Simplified Single-Phase Multistring Multilevel Inverter Topology for DistributedEnergy Resources", PP. 1-6, 2011.

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 8, August 2013

#### **BIOGRAPHY**

Mr. K. Lakshmi Ganesh obtained his Bachelor of Technology in Electrical and Electronics Engineering from Anurag Engineering College, Kodad, Andhra Pradesh. He completed Master of Technology in Power Electronics from Sri Vasavi Engineering College, Andhra Pradesh, India. His areas of interest include multilevel inverters and Electrical Machines. He is currently working as Assistant Professor in the Electrical and Electronics Engineering Department in Vishnu Institute of Technology, Bhimavaram, W.G.Dist, Andhra Pradesh, India.

Mr.M.balaji obtained his Bachelor of Technology in Electrical and Electronics Engineering from Swarnandhara College of engineering and technology, Narasapuram, Andhra Pradesh, India. He completed his Master of Technology in Power systems in NIT CALICUT, India. His area of interest includes Multilevel Inverters and Neural networks Fuzzy logic and FACTS. He is currently working as Assistant Professor in Electrical and Electronics Engineering Department at Vishnu institute of Technology Bhimavaram, Andhra Pradesh, India

Mr.K.N.S.Durga Prakash obtained his Bachelor of Technology in Electrical and Electronics Engineering from Swarnandhara College of engineering and technology, Narasapuram, Andhra Pradesh, India. He completed his Master of Technology in Power Electronics in Sri Vasavi Engineering College, Andhra Pradesh, India. His area of interest includes Multilevel Inverters, Power Systems and Power quality management. He is currently working as Assistant Professor in Electrical and Electronics Engineering Department at Vishnu institute of Technology Bhimavaram, Andhra Pradesh, India.