> (An ISO 3297: 2007 Certified Organization) Vol. 3, Issue 3, March 2014

# Bus Energy Minimization for a Serial Link by Modified Embedded Transition Inversion Coding

J. Jenifa<sup>1</sup>, C.Jacob Ebbipeni<sup>2</sup>, V.Monisha<sup>3</sup>,

PG Student, ME - VLSI Design, Dr. SACOE, Tiruchendur, Tamilnadu, India<sup>1</sup>

PG Student, ME - VLSI Design, Sri Venkateswara College of Engineering and Technology, Tirupachur,

Tamilnadu, India<sup>2</sup>

Assistant Professor, Department of ECE, Dr. SACOE, Tiruchendur, Tamilnadu, India<sup>3</sup>

**ABSTRACT**: In all type of electronic circuits, reducing the energy dissipation is one of the major topics of interest. In bus interconnect lines, the dynamic power dissipation contributes a significant fraction in the overall power dissipation. Hence, the main objective of VLSI designers is to minimize the power dissipation, switching activity, on the interconnect lines. A modified Embedded Transition Coding Scheme reduces the number of bus lines in conventional parallel-line bus by multiplexing each m-bits onto a single line is proposed. The advantage of Serial Line Bus is that they have fewer lines, reducing crosstalk and area. Serializing parallel buses tends to increase bit transition and power dissipation. The proposed Embedded Transition Inversion Coding method uses an efficient encoding and decoding technique in order to minimize the transition activity and power consumption in serial links. In previous method a transition indication bit is added in every data word to represent a inversion indication. This extra bit increases the number of transmitted bits, number of bit transitions and power dissipation. This proposed coding scheme is used to solve the issue of the extra indication bit. This scheme eliminates the need of sending an extra bit by embedding the inversion information in the phase difference between the clock and the encoded data. In this proposed method Alexander Phase Detector is replaced by Half Rate Phase Detector. The proposed system is simulated by using Xilinx 13.1 software to get efficient output. The proposed system result analysis shows better than the existing method.

**KEYWORDS:** Serial Interconnection, Embedded Transition Inversion (ETI) coding, Phase Encoder, Phase Detector, Bit two inverter.

### I. LITERATURE SURVEY

Parallel buses multiplexed into a serial link enables an improvement in terms of reducing interconnect area, coupling capacitance, and crosstalk [1], but it increases the overall switching activity factor (AF) and energy dissipation. Therefore, an efficient coding method needed to reduce the switching AF is an important issue in serial interconnect design. Existing methods solves the problem of increased switching activity for the parallel buses. A bus-invert method [2] minimizes the switching activity for the parallel buses. This method transmits the original or inverted data to minimize power dissipation and switching activity. Improved bus-invert coding methods such as the partial bus-invert coding [3] and weight-based bus invert coding methods[4]reduces power dissipation. But it uses extra control bit to send the inversion indication signal. It increases extra transmission line. Extra channel problem is solved by the serial coding technique[5]. In this method an extra information bits are added to the back of the original data word. It solves the area overhead problem. But it increases data latency. To reduce power dissipation Joint crosstalk avoidance code and error correction code[7] are proposed. Combining serializing bus with the error correction code joint crosstalk avoidance code and error correction code[8] is proposed to reduce the power. Transition inversion coding (TIC) [9] technique reduces switching activity for random data and to detect errors. An extra transition indication bit is added in every data word. This extra bit not only increases the number of transmitted bits, but also increases the transitions and latency.

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 3, March 2014

### **II.INTRODUCTION**

Power dissipation is a major critical design criterion in most system designs, especially in portable battery-driven applications. With the increasing drive towards System On Chip (SOC) applications, power has become an important parameter that needs to be optimized along with speed and area. The main sources of power dissipation in VLSI circuits are the leakage currents, the stand-by current, the short-circuit current, and the capacitance current (due to charging and discharging of node capacitances during transitions). The major source of power dissipation is given by,

$P = \frac{1}{2} C_L V_{dd}^2 E(sw) f_{clk}$

where,P is the capacitive power dissipation  $C_L$  is capacitance at the output of the node  $V_{dd}$  is the supply voltage  $f_{clk}$  is the clock frequency E(sw) is the average number of output transitions

Serialization reduces the number of wires and leads to a larger interconnect width and spacing. A large interconnect spacing reduces the coupling capacitance, while the wider interconnects reduce the resistivity. A significant improvement in the interconnect energy dissipation is achieved by applying different coding schemes and their proposed multiplexing techniques. However, the power reduction decreases when the degree of multiplexing increases. The Modified Embedded Transition Inversion (ETI) Coding scheme solves the issue of the extra indication bit. This scheme eliminates the need of sending an extra bit by embedding the inversion information in the phase difference between the clock and the encoded data. When there is an inversion in the data word, a phase difference is generated between the clock and data. Otherwise, the data word remains unchanged and there is no phase difference between the clock and the data. The receiver side adopts a phase detector (PD) to detect whether the received data word has been encoded or not. Simulation results shows that the proposed coding scheme has low transitions for different kinds of data patterns.

#### **III.EFFICIENT COMMUNICATION**

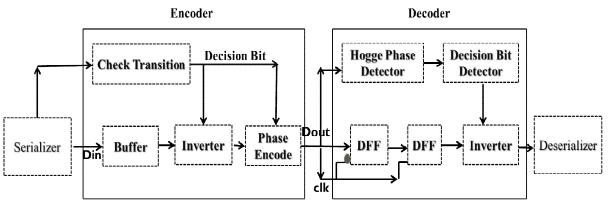

The architecture of the Modified ETI Encoding and the Decoding Scheme is shown in Fig. 5.

Fig. 5 Architecture of the modified ETI scheme

### A. ETI Encoder

The ETI encoder includes the check transitions block, buffer, B2INV, and phase encoder. The check transition block is shown in Fig. 6. In the ETI encoder part, the input data are stored in the buffer and wait for the check transition

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 3, March 2014

operation is completed. The number of transition and threshold value in a data word are used to set the decision bit. The decision bit is used to control the encoding process in the inverter and the phase encoder block.

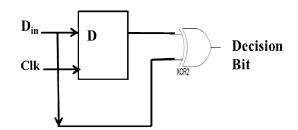

Fig. 6 Check Transition Block

The check transition circuit counts the transition in the data word. A transition between two bits is calculated by performing the XOR between them. D-FF stores the previous bit, the XOR operation is performed between the previous bit and the present bit. The WL indicator block counts the length of the data word. It generates a high signal at the first bit of the data word to reset the adder and the D-flip-flop. The number of transition in a data word is counted in the adder and sets the decision bit to high when the  $N_t \ge N_{\text{th}}$ . If the decision bit is set to 1 the input data becomes inverted. The decision bit is used to control the encoding process in the inverter and the phase encoder block. When the decision bit is zero, the inverter passes the non-inverted bit stream. Otherwise, the bit stream is encoded.

The inversion encoding operation can be expressed as

$be_1 = b_1$   $be_2 = b_2, \quad \text{with } N_t < N_{\text{th}}$  $!b_2, \quad \text{with } N_t \ge N_{\text{th}}.$

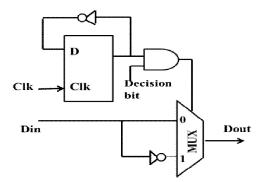

The inverter block is shown in the Fig.7

Fig. 7 Bit Two Inverter

The phase generator is used to generate phase difference between the encoded data and the clock. Depending on the encoded data, there are three types of phase encoding: the one cycle delay, the half cycle delay and the special data word. The phase encoder is shown in the Fig. 8.

(An ISO 3297: 2007 Certified Organization)

Fig. 8 Phase Encoder

#### B. ETI Decoder

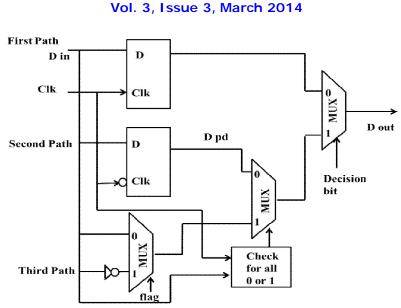

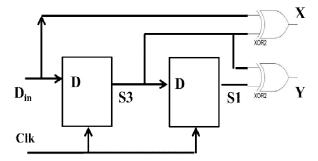

The ETI encoder generates the phase difference between the clock and the data word. A PD identifies an early or delayed phase. Modified ETI Coding scheme adopts the Hogge Phase Detector [13]. The PD is shown in Fig. 9.

Fig. 9Hogge Phase Decoder

The PD is controlled by the clock CK and input data Din. PDs for random data must provide two essential functions. Data transition detection and Phase difference detection occurs when the clock CK and input data Din are valid, the PD is activated to identify the phase relation between the clock and the data. The PD can determine whether a data transition exists from the condition that the clock leads or lags the data. The decision bit is used in the inverter for the decoding. The decoding operator in the inverter is the same as that in the encoder. The phase detector identifies whether the encoded data from the encoder block is encoded data or unencoded data depending on the decision bit.

The inversion decoding operation for the decoded output  $bd_1bd_2$  is  $bd_1 = be_1$  $bd_2 = be_2$ , with Nt < Nth  $!be_2$ , with  $Nt \ge N$ th.

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 3, March 2014

If the decision bit is set to zero the data from the encoder block is unencoded data. if the decision bit is set to one the data from the encoder block is the encoded data. After decoding operation the datas are parallized in the deserializer.

### IV.SIMULATION RESULTS AND DISCUSSION

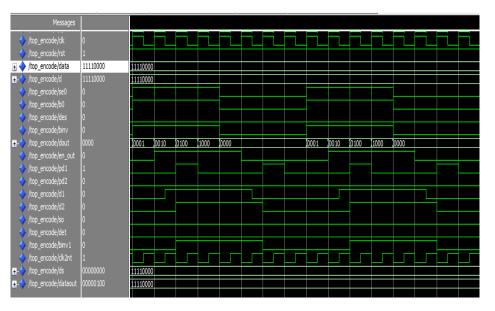

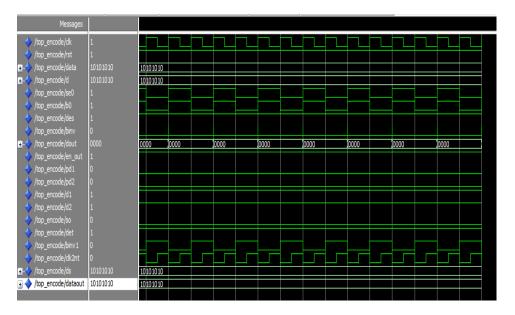

The snapshot shown in figure is taken from the modelsim 6.a software which shows the 8-bit data encoding and decoding using Modified ETI Algorithms for the input data's 1111000 and 10101010 respectively.

Fig. 9. 8 bit Modified ETI Coding for the input 11110000

Fig.10 8 bit Modified ETI Cooding for the input 10101010

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 3, March 2014

For the input data 1111000 as shown in the Fig 9 the number of transition is 1 (Nt=1). The threshold value is set as half the bus word length (Nth=4). Here the number of transition is 1 less than the threshold value 4. Hence there is no need for encoding the input data. The original data is sent as it is.

For the input data 10101010 as shown in the Fig 10 the number of transition is 1 (Nt=7). The threshold value is set as half the bus word length (Nth=4). Here the number of transition is 7 greater than the threshold value 4. Hence the input data need to be encoded to reduce the switching activity. So the original data is inverted and then phase encoded in the encoder block and then it is transmitted to the channel. At the receiver block the encoded input data is phase decoded and inverted to get the original output value.

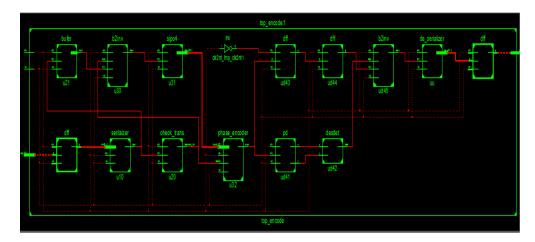

Register Transfer Logic (RTL) representation of the Modified ETI scheme is shown in the Fig 11.

Fig. 11 RTL Schematic for the Modified ETI scheme

### V. COMPARATIVE ANALYSIS

Comparative analysis of ETI encoding and decoding Scheme and Modified ETI encoding decoding scheme can be done by the device utilization summary extracted from Xilinx. Device utilization summary is the report of used device hardware in the implementation of the chip such as RAM, ROM, slices, flip flops etc. Synthesis report shows the complete details of device utilization as total memory utilization. The device targeted for synthesis on SPARTEN-3 FPGA . Table 1 compares the hardware utilization for ETI encoder decoder and the Modified Encoder decoder scheme. Selected Device: 3s100etq144-4

| Device Part                  | Existing ETI Scheme |           | Modified ETI Scheme |      |           |             |

|------------------------------|---------------------|-----------|---------------------|------|-----------|-------------|

|                              | Used                | Available | Utilization         | Used | Available | Utilization |

| Number of Slices             | 37                  | 960       | 3.9%                | 34   | 960       | 3.5%        |

| Number of Slice Flip<br>Flop | 55                  | 1920      | 2.9%                | 41   | 1920      | 2.14%       |

| Number of 4 input<br>LUT     | 57                  | 1920      | 2.96%               | 43   | 1920      | 2.2%        |

| Number of bonded<br>IOB's    | 18                  | 108       | 16.66%              | 18   | 108       | 16.66%      |

| Number of GCLKs              | 1                   | 24        | 4.16%               | 1    | 1         | 4.16%       |

TABLE I.

HARDWARE UTILIZATION OF EXISTING ETI AND MODIFIED ETI

(An ISO 3297: 2007 Certified Organization)

#### Vol. 3, Issue 3, March 2014

TABLE II.

POWER ANALYSIS OF EXISTING AND MODIFIED ETI CODING SCHEMES

| Parameter         | Existing ETI<br>Scheme | Modified<br>ETI Scheme |  |

|-------------------|------------------------|------------------------|--|

| Power Dissipation | 0.761 nw               | 0.654 nw               |  |

#### VI.CONCLUSION

Existing ETI coding and the Modified ETI coding is implemented in Xilinx 13.1 and functionally checked in Modelsim 6.a software. A comparative analysis is done with respect to hardware utilization. This scheme eliminates the need of sending an extra bit by embedding the inversion information in the phase difference between the clock and the encoded data thereby reducing the extra bit transition and switching activity. The proposed Modified ETI Coding scheme is reduces the switching activity and power compare with the existing ETI scheme. The proposed technique is suitable for most of the Low Power VLSI applications.

#### References

- K. Lee, S. J. Lee, and H. J. Yoo, "SILENT: Serialized low energy transmission coding for on-chip interconnection networks," in Proc. IEEE Int. Conf. Comput.-Aided Design Conf., pp. 448–451, Nov. 2004.

- [2] M. R. Stan and W. P. Burleson, "Bus-invert coding for low-power I/O," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 3, no. 1, pp. 49–58, Mar. 1995.

- [3] Y. Shin, S. I. Chae, and K. Choi, "Partial bus-invert coding for power optimization of application-specific systems," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 9, no. 2, pp. 377–383, Apr. 2001.

- [4] R. B. Lin and C. M. Tsai, "Weight-based bus-invert coding for lowpower applications," in Proc. Int. Conf. VLSI Design, pp. 121–125, Jan. 2002.

- [5] C. H. Kuo, W. B. Wu, Y. J. Wu, and J. H. Lin, "Serial low power bus coding for VLSI," in Proc. IEEE Int. Conf. Commun., Circuits Syst., pp. 2449–2453, Jun. 2006.

- [6] S. Zogopoulos and W. Namgoong, "High-speed single-ended parallel link based on three-level differential encoding," IEEE J. Solid-State Circuits, vol. 44, no. 2, pp. 549–558, Feb. 2009.

- [7] S. R. Sridhara and N. R. Shanbhag, "Coding for reliable on-chip buses: A class of fundamental bounds and practical codes," IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 26, no. 5, pp. 977–983, May 2007.

- [8] P. T. Huang, W.-L. Fang, Y.-L. Wang, and W. Hwang, "Low power and reliable interconnection with self-corrected green coding scheme for network-on-chip," in Proc. 2nd ACM/IEEE Int. Symp. Netw. Chip, pp. 77–84, Apr. 2008.

- [9] R. Abinesh, R. Bharghava, and M. B. Srinivas, Transition inversion based low power data coding scheme for synchronous serial communication," in Proc. IEEE Comput. Soc. Annu. Symp. VLSI Conf., pp. 103–108, May 2009.

- [10] S. J. Lee, S. J. Song, K. Lee, J. H. Woo, S. E. Kim, B. G. Nam, and H. J. Yoo, "An 800 MHz star-connected on-chip network for application to systems on a chip," in IEEE Int. Solid-State Circuits Conf. Technol. Dig., pp. 468–469, Feb. 2003.

- [11] K. Lee, S. J. Lee, and S. E. Kim, "A 51 mW 1.6 GHz on-chip network for low-power heterogeneous SoC platform," in Proc. IEEE Int. Solid-State Circuits Conf., pp. 152–518, Feb. 2004.

- [12] K. Lee, S. J. Lee, and H. J. Yoo, "Low-power network-on-chip for highperformanceSoC design," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 2, pp. 148–160, Feb. 2006.

- [13] B. Razavi, "Challenges in the design of high-speed clock and data recovery circuits," IEEE Commun. ag., vol. 40, no. 8, pp. 94–101, Aug. 2002.

- [14] R. Abinesh, R. Bharghava, and M. B. Srinivas, "Transition inversion based low power data coding scheme for synchronous serial communication," in Proc. IEEE Comput. Soc. Annu. Symp. VLSI Journal., pp. 103–108, May 2009.

- [15] Brajesh Kumar Kaushik n, Deepika Agarwal, Nagendra G. Babu "Bus encoder design for reduced crosstalk, power and area in coupled VLSI interconnects" Microelectronics Journal. Elsevire April 2013.

- [16] J. Bhasker "VHDL Primer", third edition.

- [17] M. Ghoneima, Y. Ismail, M. Khellah, J. Tschanz, and V. De, "Serial-link bus: A low-power on-chip bus architecture," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 9, pp. 2020–2032, Sep. 2009.