# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 9, September 2013

# Complementary Metal Oxide Semiconductor Image Sensor

Salil Bhalla<sup>1</sup>, Kulwinder Singh Monga<sup>2</sup>, Rahul Malhotra<sup>3</sup>

Student, Bhai Maha Singh College of Engineering, Muktsar, Punjab, India<sup>1</sup>

Assistant Professor, Bhai Maha Singh College of Engineering, Muktsar, Punjab, India<sup>2</sup>

Director-Principal, Adesh Institute of Technology, Chandigarh, India<sup>3</sup>

Abstract: In this paper an advanced algorithm of online image memory size compression has been introduced. The whole process of online image memory size compression is divided into 3 steps. These are 1) Image capture 2) Pixel level Image compression 3) Image mapping and storage. A block based compression algorithm is being proposed in this. The brightest pixel value is choosen first of all and then all the pixel values of the block are compared with the pixel value of reference pixel. After that a comparator circuit is being employed so that in consonance with the proposed mapping the differential values of the successive pixels are further compared through comparator circuit. And then selected number of differential values are calculated and quantized using intermediate precision bits. Thus the bits required for on-pixel memory storage are reduced. This enables reduced silicon area for System on chip. Mentor Graphics' Design Architect tool is being used to synthesize the algorithm.

Keywords: Compressive sensing, Digital pixel sensors (DPSs), Block – Based compression algorithm.

### I. INTRODUCTION

The history of image processing technology in electronics dates from the invention of television system in 1927 [5]. From this time, the image processing technology has been studied and developed mainly in terms of television broadcasting technology, such as NTSC or PAL.

On an image capturing devices, the solid-state imagers have been invented in 1970s, which employ the CCD (charge coupled device) as a signal transformer [6]. The recent development of VLSI technologies enables us to fabricate not only photo-detectors and signal transfer circuits, but also a simple image processing circuits in one image sensor chip, so called computational sensors [7].

Image sensors are basically distinguished by their pixel sensors i.e. whether it is active pixel sensor or passive pixel sensor [8]. Passive imagers require less amount of MOS devices or lesser silicon area but correspondingly active pixels with a trade-off provides batter picture quality. Hence, most of image sensors are active pixel image sensor.

However the history of CMOS active pixel sensors is not as long as it is for CCD active pixel sensors. First research paper on CMOS image sensor in IEEE Xplorer was published on 'A CMOS facsimile video signal processor' [9] in 1985. From the introduction of CMOS in image sensors, it is used in image processing as analog pixel part or as a processor. In image sensors introduction of image sensor reduces power dissipation, improve switching capability and helpful in analog to digital conversion due to its switching capability.

In 1994, CMOS image sensors were reported to be described in the concept of image compression [10]. A CMOS photodiode was used to reduce the dynamic range [11], as reduced dynamic range require lesser number of bits for digital data storage. So from that on the concept of compression or rather on-pixel compression was directly linked with dynamic range of frame. However, various algorithms and methodologies were applied to reduce the dynamic range but one commonly used methodology was to capture >> store >> compress technique. There are various hardware friendly algorithms [12] designed for such methodology.

In modern era a new methodology of image acquisition and online image compression is used and being implemented, it is capture >> compress >> store [13]. As this approach of image compression is newer one, hence there is not much work reported in this area. Due to its enhanced results over old methodology, this technique has large potential of research.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

# Vol. 2, Issue 9, September 2013

#### II. DESIGN ALGORITHM

### A. Block-Based Compression

In various image compression algorithms whole image captured by optical device is divided into blocks instead of using whole image. The concept of block-based compression enables a reduced dynamic range of differential pixel values for adaptive quantization.

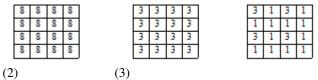

Here are some block-level distributions of image.

Fig1. Bits distribution per pixel for different algorithms

- (1) In this block representation all pixels are provided with a full precision of 8-bits to each pixel. Such kind of distribution is treated as original image acquisition.

- (2) In this block representation we choose the brightest pixel value in the block and provide it full precision of 8-bits. While all other pixels are captured with an inter-mediate precision of 3 bits. As the brightest pixel value represents the highest intensive pixel, so comparing the brightest pixel with neighbouring pixel will provide a reduced dynamic range. A reduced dynamic range is so as captured with reduced number of bits.

- (3) This is the proposed image compression algorithm, in which the brightest pixel is captured with full precision of 8-bits. And then after the block is sub-divided into smaller blocks (e.g. 2×2). The pixel of each sub block is captured as differential pixel value with an inter-mediate precision of 3-bits. While next pixel is stored with 1-bit. The differential values of previous pixel and current pixel are compared using a comparator [29]-[30], and 1-bit output of comparator is stored.

### B. Mapping of pixels

(1)

In the mapping of pixels it is compulsory to trace the flow of data at pixel and block level. Here is an introductory data flow block representation.

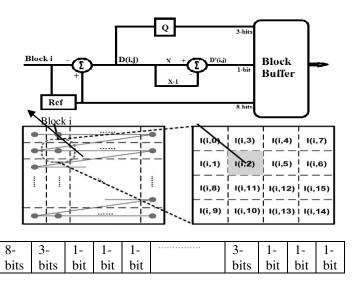

Fig2. Architecture of the block buffer

The mapping of pixels in image acquisition helps to optimize the image compression. Here are some examples of different kind of mapping usually found in image compression algorithms.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 9, September 2013

### Linear scanning

In linear scanning, image pixels are scanned row wise i.e. first of all first row of pixels will be scanned and then after it moves to next row within a block as shown in Fig. 2.4 and blocks are also scanned in similar fashion [23].

| I(i, <del>0)</del>  | I(i,1)  | I(i,2)  | <b>L</b> (i,3)  |

|---------------------|---------|---------|-----------------|

| I(i,4)              | 1(1,5)  | I(i,6)  | <u>I(i,</u> 7)  |

| I(i, <del>8)</del>  | 1(1,5)  | I(i,10) | <u>(i,</u> 11)  |

| I(i, <del>12)</del> | 1(1,13) | I(i,14) | <u>I(i,</u> 15) |

Fig3.1. Linear scanning of pixels within a block

#### Linear sub-block scanning

In linear sub-block scanning, whole block is firstly sub divided in 2×2 blocks and then performs linear scanning sub-block wise instead of block wise as shown in Fig. 2.5 [14].

| I(i, <del>0)</del> | <del>(i,</del> 1) | I(i,4) I(i,5)               |  |

|--------------------|-------------------|-----------------------------|--|

| I(i,2)             | I(i,3)            | I(i,j) = I(i,7)             |  |

| I(i,8)             | (,9)              | I(i, <del>12)</del> I(i,13) |  |

| I(i,10)            | I(i, 11)          | I(i,11) I(i,15)             |  |

Fig3.2. Linear sub-block scanning

| I(i 0) | I(i 3)             | I(i,4)  | <b>I</b> (i 7)     |

|--------|--------------------|---------|--------------------|

| I(i,1) | I(i,2)             | I(i 5)  | I(i,6)             |

| I(i 8) | <del>I(i</del> 11) | I(i,12) | <del>I(i</del> 15) |

| I(i,9) | I(i,10)            | I(i,13) | I(i,14)            |

Fig3.3. Hilbert mapping of pixels.

In Hilbert mapping, image pixels are addressed as per Hilbert curve. However Hilbert mapping help improve in reducing the temporal and spatial redundancies. And also provides a good speed of sampling. But Hilbert mapping changes with number of pixels per block and also with number of blocks per frame. And also this mapping scheme is not regular one for each sub block [15].

| I(i 0) | I(i <mark>.3)</mark>  | <u>I(i</u> 4)      | <del>I(i</del> 7) |

|--------|-----------------------|--------------------|-------------------|

| I(i,1) | I(i 2)                | 1(i,5)             | <b>I</b> (i,6)    |

| I(i 8) | I(i <mark>.11)</mark> | <del>I(i</del> 12) | I(i 15)           |

| I(i,0) | I(i,10)               | I(i,13)            | <u>I(i,</u> 14)   |

Fig3.4. Proposed pixel mapping

In our proposed pixel mapping we will select the brightest pixel value from the block and provide it full precision of 8-bits. Then after we will calculate differential pixel values by comparing reference pixel with other pixel and store the differential values using a 3 bit precision. The remaining pixels are compared differential pixel values previous differential value and current differential value. These pixels are stored using 1-bit precision.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 9, September 2013

III. SYNTHESIS RESULTS

# TABLE I

SIMULATION RESULTS FOR A CROPPED  $20 \times 32$  PIXEL CAMERAMAN IMAGE OF A PRECISION OF 8-BITS PER PIXEL

| Testing samples               | Bloc<br>k size | Quantizer<br>bits | PSNR (dB) | Bits per<br>block |

|-------------------------------|----------------|-------------------|-----------|-------------------|

| Cameraman<br>cropped<br>image | 4              | 3                 | 20.52     | 32                |

| Cameraman<br>cropped<br>image | 4              | 4                 | 21.21     | 36                |

## A. Synthesis results

In the synthesis of our algorithm firstly we design a pixel level CMOS Active Pixel circuit. As per the requirement of our algorithm we design this circuit. After designing the pixel level circuit we form a block level arrangement of pixels for testing.

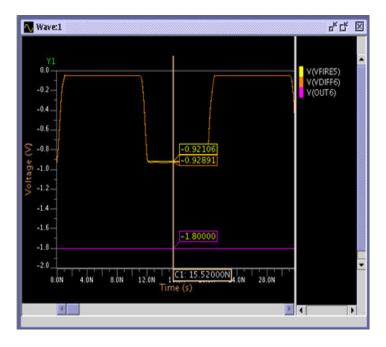

The dynamic range of differential pixel output can be then arbitrated from the synthesis of whole block. Figure 4 shows the output for the Pixel 2, where Vfire and Vdiff2 are inputs to comparator of pixel 2 and Vout2 is output of pixel 2. By the analysis of an ordinary photodiode following data comes in existence.

TABLE II

SHORT CIRCUITED CURRENT, OPEN CIRCUITED VOLTAGE AND INPUT INTENSITY RELATIONSHIP FOR AN ORDINARY PHOTODIODE

| Light            | Intensity        | Current             | Voltage    |

|------------------|------------------|---------------------|------------|

|                  | $(\mathbf{l_x})$ | $(\mathbf{I_{sc}})$ | $(V_{oc})$ |

| Direct sunlight  | 1000             | 30 uA               | 500 mV     |

| Overcast day     | 100              | 3 uA                | 440 mV     |

| Twilight         | 1                | 0.03 uA             | 310 mV     |

| Full moon night  | 0.1              | 3000 pA             | 280 mV     |

| Clear night / no | 0.001            | 30 pA               | 250 mV     |

| moon             |                  |                     |            |

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

# Vol. 2, Issue 9, September 2013

Fig4. Pixel 6 outputs, where  $V_{diff5}$  and  $V_{diff6}$  are inputs to comparator of pixel 2 and  $V_{out6}$  is output of pixel 6.

### IV. ALGORITHM IMPLEMENTATION

#### A. Overview

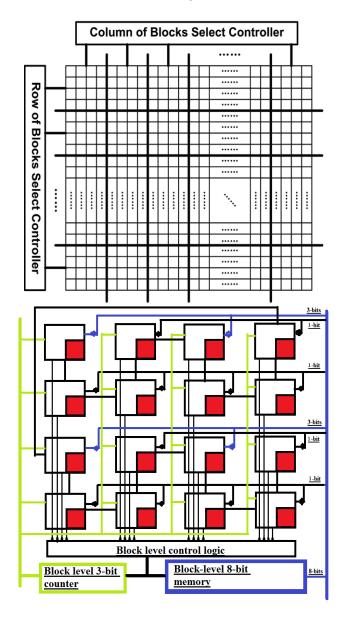

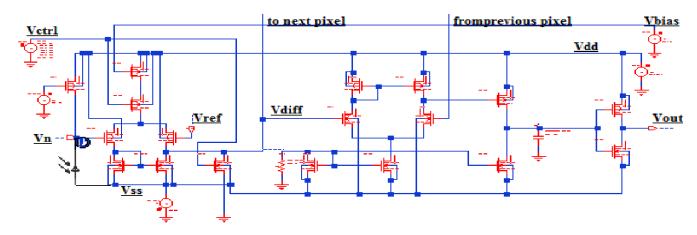

Fig5. Illustrates the architecture of overall system. The sensor array is divided into 4×4 blocks. A single pixel consists of a MOS switch, a photodiode, a differential amplifier stage, and a comparator. As shown in Fig.5 whole image is divided into small blocks, and for smooth mapping of pixels and blocks controller bits are required. There are two blocks select controllers i.e. row blocks select controller and column blocks select controller. Memory size of these controllers varies with respect to size of block. This is the block based representation of image. However in block based architecture it is also quite possible to compress the image and store it with reduced number of bits. Hence various decomposition theorems are here to compress the image at block level prior to storage like QTD i.e. quadrant tree decomposition A MOS switch is used to level up Vn voltage to Vdd. And also a MOS switch distinguishes one frame with another and hence reduces power dissipation. A photodiode is used as a sensor device which converts light intensity into equivalent voltage as described in TABLE II. Hence voltage at node Vn will be proportional to light intensity.

In our design we use 3-4 bits counter to count the differential pixel values and correspondingly store them in onchip memory.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

# Vol. 2, Issue 9, September 2013

- (B) 4×4 Bloc

- (A) Sensor Array

# International Journal of Advanced Research in Electrical, **Electronics and Instrumentation Engineering**

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 9, September 2013

#### (C) Pixel

Fig5. Overview of the overall system (a) Architecture of the sensor array. (b) Architecture of one block. (c) Circuit diagram of one pixel.

#### V. CONCLUSION

In this paper, online image compression concept is adduced and is synthesized using Mentor Graphics Design Architect tool. The paper illustrates the advantages of proposed algorithm 1) reduced silicon area required for DPS; 2) improved fill-factor; 3) online compression processing, which enables the concept of parallel processing. Results illustrate that the proposed algorithm results in more than 50% on chip memory

### VI.FUTURE WORK

This work was synthesized using Design tools, however capturing images using camera and processing images on hardware implemented design may provide enhanced results.

### REFERENCES

- L. H. Croft and J. A. Robinson, "Subband image coding using watershed and watercourse lines of the wavelet transform," IEEE Trans. Image [1] Process., vol. 3, no. 6, pp. 759–772, Nov. 1994.

- B. Wu and C. Lin, "Memory-efficient architecture for JPEG 2000 coprocessor with large tile image," IEEE Trans. Circuits Syst. II, Exp. [2] Briefs, vol. 53, no. 4, pp. 304-308, Apr. 2006.

- [3] Y. Li and M. Bayoumi, "VLSI architectures for JPEG 2000 EBCOT," in Proc. 14th Asilomar Conf. Signals, Syst. Comput., Oct.-Nov. 2006, pp. 907-911.

- L. Liu, N. Chen, H. Meng, L. Zhang, Z. Wang, and H. Chen, "A VLSI architecture of JPEG2000 encoder," IEEE J. Solid-State Circuits, vol. 39, no. 11, pp. 2032-2040, Nov. 2004.

- S. Matsubara and H. Hikawa, "Hardware friendly vector quantization algorithm," in Proc. IEEE Int. Symp. Circuits Syst., May 2005, vol. 4, pp. 3623-3626.

- H. Eeckhaut, H. Devos, B. Schrauwen, M. Christiaens, and D. Stroobandt, "A hardware-friendly wavelet entropy codec for scalable video," in Proc. IEEE Design, Autom. Test Eur., 2005, vol. 3, pp. 14–19.

- [7] A. K. Gupta, D. Taubman, and S. Nooshabadi, "Near-optimal low-cost distortion estimation technique for JPEG2000 encoder," in Proc. IEEE Int. Conf. Acoust., Speech Signal, May 2006, vol. 3, pp. III-14-III-19.

- L. Liu, H. Meng, and M. Zhang, "An ASIC implementation of liftingbased 2-D discretewavelet transform," in Proc. IEEE Asia Pacific Conf. Circuits Syst., Dec. 2006, pp. 271-274.

- G. Iddan, G. Meron, A. Glukhovsky, and P. Swain, "Wireless capsule endoscopy," Nature, vol. 405, pp. 417-418, May 2000.

- [10] M. Tubaishat and S. Madria, "Sensor networks: An overview," Potentials, vol. 22, no. 2, pp. 20–23, Apr./May 2003.

- [11] B. S. Carlson, "Comparison of modern CCD and CMOS image sensor technologies and systems for low resolution imaging," in IEEE Proc. Sens., Jun. 2002, vol. 1, pp. 171–176.

- [12] A. Theuwissen, "CMOS image sensors: State-of-the-art and future perspectives," in Proc. 37th Eur. Solid State Device Res. Conf., Sep. 2007,

- pp. 21–27. S. Kleinfelder, S. Lim, X. Liu, and A. El Gamal, "A 10000 frames/s CMOS digital pixel sensor," IEEE J. Solid-State Circuits, vol. 36, no. 12, pp. 2049-2059, Dec. 2001.

- A. El Gamal, D. Yang, and B. Fowler, "Pixel level processing—Why, what and how?," in Proc. SPIE, Jan. 1999, vol. 3650, pp. 2-13.

- A. El Gamal, D. Yang, and B. Fowler, "Pixel-level processing: Why, what, and how?," in Proc. SPIE, Sens., Cameras, Appl. Digital Photography, Mar. 1999, vol. 3650, pp. 2–13.

# International Journal of Advanced Research in Electrical, **Electronics and Instrumentation Engineering**

(An ISO 3297: 2007 Certified Organization)

# Vol. 2, Issue 9, September 2013

- [16] D. Renshaw, P. B. Denyer, G. Wang, and M. Lu, "ASIC image sensors," in Proc. IEEE Int. Symp. Circuits Syst., May 1990, vol. 4, pp. 3038-3041.

- [17] X. D. Wu, R. A. Street, R. Weisfield, S. Ready, and S. Nelson, "Pagesized a-Si:H 2-dimensional array as imaging devices," in Proc. 4th Int. Conf. Solid-State Integr. Circuit Technol., Oct. 1995, pp. 724-726.

- [18] P. J. W. Noble, "Self-scanned silicon image detector arrays," IEEE Trans. Electron Devices, vol. ED-15, pp. 202–209, Apr. 1968. [19] E. R. Fossum, "Active pixel sensors: Are CCD's dinosaurs?," Int. Soc. Opt. Eng., vol. 1900, pp. 2–14, Jul. 1993.

- [20] F. Andoh, H. Shimamoto, and Y. Fujita, "A digital pixel image sensor for real-time readout," IEEE Trans. Electron Devices, vol. 47, no. 11, pp. 2123–2127, Nov. 2000.

- [21] S. Chen, A. Bermak, Y. Wang, and D. Martinez, "Adaptive-quantization digital image sensor for low-power image compression," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 54, no. 1, pp. 13-25, Jan. 2007.

- [22] C. Lai, Y. King, and S. Huang, "A 1.2-V 0.25-..mclock output pixel architecture with wide dynamic range and self-offset cancellation," IEEE Sensors J., vol. 6, no. 2, pp. 398–405, Apr. 2006.

- [23] B. Mansoorian, H. Yee, S. Huang, and E. Fossum, "A 250 mW, 60 frames/s 1280..720 pixel 9 b CMOS digital image sensor," in Proc. IEEE Int. Solid-State Circuits Conf., Feb. 1999, pp. 312-313.

- [24] Q. Luo, Z. J. Chen, J. G. Harris, S. Clynes, and Erwin, "Adaptive relative and absolute address coding CMOS imager technique and system architecture," U.S. Patent 7071982B2, Jul. 2006.

- [25] V. Vorperian, "Simplified analysis of PWM converters using the model of the PWMswitch. Part I: Continuous conduction mode," IEEE Trans. Aerosp. Electron. Syst., vol. 26, no. 5, pp. 490-496, May 1990.

- [26] A. Bermak, "ACMOS imager with PFM/PWM based analog-to-digital converter," in Proc. IEEE Int. Symp. Circuits Sys., May 2002, vol. 4, pp. IV-53-IV-56.

- [27] M. Zhang and A. Bermak, "A low power CMOS image sensor design for wireless endoscopy capsule," in Proc. IEEE Biomed. Circuit Syst. Conf., Nov., 2007, pp. 2355-2358.

- [28] Milin Zhang and Amine Bermak, "Compressive Acquisition CMOS Image Sensor: From the Algorithm to Hardware Implementation", VOL. 18, pages 490-500 NO. 3, MARCH 2010.

- P.E. Allen and D.R. Holberg, "CMOS Analog Circuit Design 2nd Ed", Oxford University Press, 2002.

- [30] B. Razavi, "Design of Analog CMOS Integrated Circuits", McGraw-Hill, Inc., 2001.

- [31] Sun, J.Z.; Goyal, V.K.; "Scalar Quantization for Relative Error" pp. 293-302, Apr 2011.

- [32] http://www.cis.rit.edu/class/simg712-90/notes/14-Quantization.pdf