An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

Organized by

Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

Paiyanoor-603 104, Tamil Nadu, India

# Design of Multi Value Logic Using Quantum Dot Gate FET

R.Rajith, S.Selva Prabhu

Asst. Prof, Dept.ECE SMKFIT, Chennai, Tamil Nadu

PG Student, Dept.of ECE, SMKFIT, Chennai, Tamilnadu.

Abstract—In this paper, we discuss logic circuit designs using the circuit model of three-state quantum dot gate field effect transistors (QDGFETs). QDGFETs produce one intermediate state between the two normal stable ON and OFF states due to a change in the threshold voltage over this range. We have developed circuit model which has intermediate state. Various logic can be implemented using QDGFETs. In this paper, we have discussed the designs of various three-state QDGFET combinational circuits like decoder, and comparator. Increased number of states in three-state QDGFETs will increase the number of bit-handling capability of this device and will help us to handle more number of bits at a time with less circuit elements.

*Index Terms*—QDGFET, ternary logic,field effect transistor, MVL,

# I. INTRODUCTION

Binary logic has been used for electronic designs for many decades. The challenges of the binary logic have inspired the researchers for research in multi-valued logic (MVL). For example, with binary logic designs, chip interconnects occupy so much area that it limits the performance of the VLSI chips [1]. Binary algebra also takes more digits to represents any number when compared to any higher radix algebra [2]. Going to Multi valued logic may have some efficient solutions for these challenges. Use of multi value logic ternary logic for interconnect is definitely a good way to reduce the data related metal interconnect density to half. In addition ternary logic algebra inherently processes the information for efficiently and reduced the number of transistors required to compute a calculation when compare to processing in binary logic. In ternary logic the levels are represented by 0, 1, 2, . Significant research have been done on multi valued logic and quaternary logic in past few decades [1,2]. Researchers have explored the suitable algebra for logic and arithmetic, optimized the logic algorithms, and developed the test algorithms for multi

valued logic. Though so much work has been put into research we still do not see much of implementations in MVL. One of the reasons for this is availability of suitable transistors to implement all these logic and arithmetic functions offered by the MVL research.

MVL can be implemented using different kinds of devices like resonant tunneling diodes [3], [4], resonant tunneling transistors [5]–[7], modulation-doped FETs [8]–[10], high electron mobility transistors [11]–[13], carbon nanotube field effect transistors (CNTFETs), single electron transistors (SETs), and so on. Among these semiconductor devices, CNTFET and SET are the most promising devices to implement the MVL in future.

In the CNTFET-based ternary logic circuits [14], the circuit design is based on different CNTFETs which have different threshold voltages based on the CNTs diameter thickness. Ternary logic architecture based on CNTFET is different than the conventional CMOS architecture. In the resistor-based CNTFET circuits, the value of the resistor is so high that it is difficult to fabricate. On the other hand, the conventional CNTFET-based circuit has more number of elements than that in the CMOS circuit, for example, standard ternary inverter (STI) has six CNTFETs. Besides this uniform CNTs having same diameter and similar orientation are difficult to fabricate.

On the other hand, the main problems of SET-based [15] logic implementation is lithography techniques, background charge, co-tunneling, and room temperature operation. Two major drawbacks of the SET as an electronic circuit component are, it does not have internal memory and it cannot carry DC, so that an ultrasensitive electrometer is necessary to measure its charge state

Exact copying of CMOS circuits using SET is impossible, and in order to get substantial parameter margins, even the simplest logic gates have to be redesigned. Besides this, their operation range starts shrinking under the effect of thermal fluctuations as soon as their scale  $k_B$ T reaches approximately 0.01E

Because of the presence of quantum dots in the gate region, QDGFET produces one intermediate state

An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

## Organized by

Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

## Paiyanoor-603 104, Tamil Nadu, India

between its two stable states in its transfer characteristics [16], [17]. The generation of the intermediate state can be explained by the resonant tunneling of charge carriers from the inversion channel to the quantum dots on top of the gate region. Since the quantum dots in the gate region are cladded by a high band gap insulator, charge leakage for these devices are very small, which provides the stability to the generation of the intermediate state between its normal ON and OFF states. Another advantage of QDGFET is that it can be fabricated in conventional CMOS process at room temperature. The quantum dot self-assembly is also performed at room temperature. The threshold voltage of QDGFET can be controlled easily either by varying the gate insulator thickness or varying the number of quantum dot layers on top of the gate region. The background charge problem of SET is also absent in QDGFET.

In our proposed circuit design, we use QDGFET as the key circuit element which itself can produce three states in its transfer characteristics. QDGFETs can be used in the conventional CMOS architecture to implement ternary logic circuits. The design complexity will decrease when implementing ternary logic circuits based on QDGFET.

This paper is organized as follows. Section II describes about the structure of QDGFET. Sections III and IV highlight on the theory of operation and circuit model. The inversion operation, ternary logic decoder and 1 bit ternary compatator are discussed in Sections V, VI, and VII, respectively, which is followed by the conclusions in Section VIII

## **II.QUANTUM DOT GATE FIELD EFFECT TRANSISTOR**

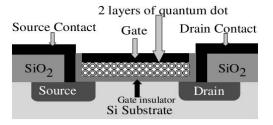

A quantum-dot gate (QDG) field-effect transistor (FET), exhibiting 3-state transfer characteristics, differs from a conventional FET as well as floating gate nanodot nonvolatile memories in its gate structure. In QDG-FETs, two or more layers of SiO<sub>x</sub> cladded Si quantum dot (or GeO<sub>x</sub> cladded Ge) quantum dots are self-assembled (as shown in Figure 1a) on top of a thin gate insulator [20, 21]. Source and drain regions are formed in quantum dot gate field effect transistor like a conventional FET. The gate tunnel insulator layer could be SiO<sub>2</sub> or HfO<sub>2</sub> or a lattice-matched epitaxial layer of high-k dielectric. Unlike floating gate QD nonvolatile memories [22-23] where the charge is permanently stored in the quantum dot layer, a three-state QDG-FET device does not have a thick outer control gate insulator layer and the charge is permitted to escape the dot via tunneling through a very thin (~1nm) SiO<sub>2</sub> cladding layer around the Si. In addition, QDG-FETs have at least two cladded quantum dot layers separated by a thin barrier that permits tunneling of Copyright to IJAREEIE

electrons. It was observed that QDG-FET structures without an outer control gate insulator (such as nitride layer) exhibit the three-state behavior.

Because of the presence of quantum dots in the gate region, QDGFET produces one intermediatestate "i" between its two stable states in its transfer characteristics. The occurrence of "i" state is explained by the transfer of the channel electrons (as a function of the gate voltage) to one of the two quantum dot layers which in turn increases the threshold voltage. An increase in the gate voltage  $V_G$  is thus compensated by an increase in the threshold voltage  $V_{TH}$ , thereby keeping  $I_D$  nearly constant. The range of gate voltage over which 'i' behavior is observed is determined by the resonant tunneling across two layers of quantum dots and the rate of electron transfer from inversion channel to dots.Fig. 1(a) shows the cross-sectional schematic of a QDGFET.

## **III. THEORY OF OPERATIONS**

In a conventional FET, the threshold voltage does not vary appreciably during operation and  $I_D$  increases with  $V_G$  as can be seen from Eq. 1.

$$I_D = \binom{W}{L} C_o \mu_n \left[ (V_G - V_{TH}) V_{DS} - \frac{V^2}{2} \right]$$

(1)

However, in a QDG-FET, an increase in the gate voltage is accompanied by an increase in the threshold voltage. This causes slow or no increase in the drain current, as the ( $V_G - V_{TH}$ ) term remains constant. In other words, increases in gate voltage are compensated by increases in the threshold voltage, and the drain current either does not increase at all or increases very slightly. This results in the manifestation of an intermediate state 'i' where the drain current virtually remains constant. The range of gate voltage in which this occurs depends on: (1) the relative location of the quantum dot energy levels with respect to the energy levels of the quantum well inversion channel, and (2) the rate of charge transfer from channel to QD layers. The tunneling probability can be expressed as [18, (2)]

$$P_{W \to d} = \frac{4\pi}{\kappa} \sum_{w,d} |\langle \Psi_d | H_t | \Psi_w \rangle|^2 (f_w - f_d) \delta(E_d - (2))$$

The charge in the gate region due to quantum dots is discrete as expressed by Eq. 3. The variation in flat band voltage  $V_{FB}$  due to the charged state of quantum dots in the gate results in corresponding change in the threshold voltage  $\Delta V_{TH}$ . The variation in the value of charge on the

www.ijareeie.com

An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

## Organized by

Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

## Paiyanoor-603 104, Tamil Nadu, India

two QD layers, as the Vg is increases, causes changes in the threshold voltage expressed in Eq. 3.

$$\Delta V_{FB} = \Delta V_{TH} = -\frac{q}{c_{zz}} \left[ \sum \frac{x_{QD1} u_1 N_{QD1}}{x_g} + \sum \frac{x_{QD2} u_2 N_g}{x_g} \right]$$

(3)

Here,  $x_{OD1}$  and  $x_{OD2}$  are the distances of quantum dot cores from the gate contact,  $n_1$  and  $n_2$  are the number of dots in layer 1 and 2, respectively, N<sub>OD1</sub> and N<sub>OD2</sub> are the charge on each SiO<sub>x</sub>-cladded Si quantum dots, C<sub>ox</sub> is the oxide capacitance (which is modified due to the presence of quantum dots). In addition,  $x_g$  is the distance of the Si- $SiO_2$  interface from the gate,  $\rho$  is the charge density and q is the electron charge.

## **IV. QDGFET CIRCUIT MODEL**

Fig.1Cross-sectional schematic of QDGFET

The effective threshold voltage is divided into three regions, OFF state, intermediate state and ON state, corresponding to the fabricated device transfer characteristics. The threshold voltage of a ODGFET can be expressed according to (4).

As the gate voltage increases, initially the threshold voltage is same as a conventional FET which is represented by V<sub>T</sub>. When the gate voltage increases through a range of voltages,  $(V_{g1} \text{ to } V_{g2})$ , the threshold voltage changes linearly with respect to the gate voltage. This changes is controlled by the  $\alpha$  parameter. With  $\alpha = 0$ , the model behaves like a conventional FET and with  $\alpha = 1$ the model has a threshold voltage that changes directly with the gate voltage which represents QDG-FET characteristics. The parameter  $\alpha$  depends on the size and number of dots which can be controlled at fabrication time, and as a result change the QD gate charge. The  $V_{g1}$ and  $V_{g2}$  terms are also determined at fabrication time. Using the equations for  $V_{Teff}$  from Eq.(4), the drain current equations can be derived using traditional MOSFET circuit modeling techniques

$$V_{Teff} = \begin{cases} V_T, V_{GS} \leq V_{g1} \\ V_T + \alpha (V_{GS} - V_{g1}), & V_{g1} \leq V_{GS} \leq (4) \\ V_T + \alpha (V_{g2} - V_{g1}), & V_{g3} > 1 \end{cases}$$

$$I_{DS} = \begin{cases} 0 & V_{SS} < V_{Teff} \\ \frac{W}{L} C_0 \mu \left( V_{\theta S} - V_{Teff} - \frac{V_{DS}}{2} \right) V_{DS}, V_{DS} < V_{\theta S} - V_{Teff} \\ \frac{W}{L} C_0 \mu \frac{\left( V_{\theta S} - V_{Teff} \right)^2}{2}, & V_{DS} > V_{\theta S} - V_{Teff} \end{cases}$$

(5)

$V_{Teff}$  = which means that When  $\alpha = 1$ .

$$I_{DS} = \frac{W}{L} C_{g} \mu \left( V_{GS} - V_{Tej} \text{ over the } V_{g1} \text{ to } V_{g2} \right)$$

region. According to this equation, IDS is independent ofV<sub>GS</sub>over thisregion, leading to a flat current curve over the region. Using these principles, the  $V_{th}$  of conventional FET is modified according to (4) in Berkeley Simulation model (BSIM 3.2.0 and BSIM 3.2.4) which is very popular for nano-FET modeling and conducted simulations of QDG-FET based

ternary logiccircuits using Cadence.

## **V. THREE STATE COMPLEMENT FUNCTION**

A ternary inversion is an operation with one input (r)and three outputs  $(l_0, l_1, and l_2)$  such that where r is the number of states in the logic space [18]. The implementation of ternary inverters requires three inverters: negative ternary inverter (NTI), STI, and positive ternary inverter (PTI), where l<sub>0</sub>, l<sub>1</sub>, and l<sub>2</sub> should be the different outputs, respectively [19]. The truth table

for these three inverters is shown in Table I.

Copyright to IJAREEIE

An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

## Organized by

Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

Paiyanoor-603 104, Tamil Nadu, India

$$l_{0} = \begin{cases} 2, & \text{if } r = 0\\ 0, & \text{if } r \neq 0 \end{cases}$$

$$l_{1} = 2 - r$$

$$l_{2} = \begin{cases} 2, & \text{if } r + 2\\ 0, & \text{if } r = 2 \end{cases}$$

$J_k$  (6)

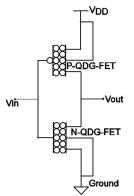

The circuit diagram of QDGFET standard ternary inverter is shown in Fig 2. This circuit is the same as a conventional CMOS inverter, except that the transistors have been replaced by QDGFETs. In this circuit, when the input is 0, the P-QDGFET is in the ON state and the N-QDGFET is in the OFF state, which makes the output 2. When the input is 2, the P-QDGFET is OFF and the N-QDGFET is ON, which make the output 0. When  $V_{in}$  is equal to 1, both transistors are in the intermediate mode, thus making both of them behave like a resistor. In this situation, the circuit behaves like a voltage divider which produces an intermediate logic output assuming both transistors have equivalent  $\beta$ s. This intermediate logic output depends on different parameters of both QDGFETs and their size ratios. In other words, changing the size ratio will produce different complement functions.

**TABLE 1.INVERTER TRUTH TABLE**

| Input | STI | PTI | NTI |

|-------|-----|-----|-----|

| 0     | 2   | 2   | 2   |

| 1     | 1   | 2   | 0   |

| 2     | 0   | 0   | 0   |

The circuit diagram for the NTI and the PTI is same as in Fig. 4(a) where the QDGFETs are replaced by conventional pMOS and nMOS transistors with 22 nm feature size parameters. Based on the threshold voltage of pMOS and nMOS, the inverter can behave as a NTI or as a PTI. For NTI, the threshold voltage of the pMOS is -0.3 V and that of the nMOS is 0.11 V. When the input voltage is below 0.11 V, the nMOS is OFF and the output is 0.5 V. When the input voltage is above 0.11 V, nMOS is ON and the output is zero. For the PTI implementation, the threshold voltage of the nMOS and the pMOS should be 0.3 V and -0.2V, respectively.

# VI. TERNARY LOGIC DECODER

Ternary decoder is a combinational circuit which decodes the input ternary signal. A ternary decoder is a one-input-three-output combinational logic circuit. The output of a ternary decoder can be represented as in (6)

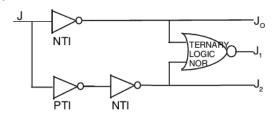

Where k =0,1,2 which corresponds to higher level (2),middle level (1), and lower level (0). The design of the ternary decoder based on QDGFET is shown in Fig. 3 where we use two NTI gates, one PTI gate, and one ternary NOR gate. The output of the decoder is shown in Fig. 4

Fig.3. Ternary logic decoder based on a QDGFET-based circuit.

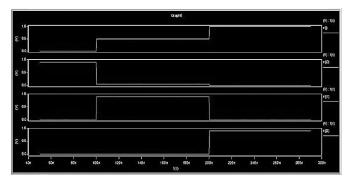

Fig.4. Input output waveforms of a ternary logic decoder

TABLE 2.NUMBER OFCIRCUITELEMENTS: CNTFET

VERSUSQDGFET

| STI |     | NANI | D/NOR | TERNARY<br>DECODER |     |  |  |

|-----|-----|------|-------|--------------------|-----|--|--|

| CNT | QDG | CNT  | QDG   | CNT                | QDG |  |  |

| FET | FET | FET  | FET   | FET                | FET |  |  |

| 6   | 2   | 10   | 4     | 16                 | 10  |  |  |

## VII. 1 BIT COMPARATOR

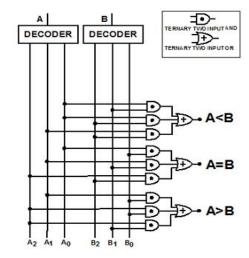

A 1-bit comparator compares two ternary bits and produces three outputs based on the relation between the two input signals. There are three outputs: A >B, A=B, and A<B in the comparator circuits. Based on the relation between two inputs (A and B), corresponding output becomes high and others remain low. The block diagram

An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

Organized by

## Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

## Paiyanoor-603 104, Tamil Nadu, India

and the input–output waveform of a ternary comparator is shown in Fig. 5 and 6, respectively. The truth table of the ternary comparator is shown in Table 2.

Table 3 shows the required number of circuit elements to implement different logic circuits using CNTFET [14] and QDGFET.

| Α | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | 2   | 0   |

| 0 | 1 | 2                                            | 0   | 0   |

| 0 | 2 | 2                                            | 0   | 0   |

| 1 | 0 | 0                                            | 0   | 2   |

| 1 | 1 | 0                                            | 2   | 0   |

| 1 | 2 | 2                                            | 0   | 0   |

| 2 | 0 | 0                                            | 0   | 2   |

| 2 | 1 | 0                                            | 0   | 2   |

| 2 | 2 | 0                                            | 2   | 0   |

Fig6.Block diagram of ternary 1-bit comparator

|                     |             |                   |      |      |      | Graphil      |      |      |      |      |      | (V) : t(I)         |

|---------------------|-------------|-------------------|------|------|------|--------------|------|------|------|------|------|--------------------|

| 1.0<br>E 0.5<br>0.0 |             |                   |      |      |      |              |      |      |      |      |      | v(#)               |

| 1.0                 |             |                   |      |      |      |              |      |      |      |      |      | (V) : t(s)<br>V(P) |

| E 05-               |             |                   |      |      |      |              |      |      |      |      |      |                    |

| 20                  | ·           |                   |      |      |      |              |      |      |      |      |      | (1):1(8)           |

| ε 1.0-<br>0.0-      |             |                   |      |      |      |              |      |      |      |      |      | vput)              |

| 2.0                 |             |                   |      |      |      |              |      |      |      |      |      | (1):1(6)           |

| ε 10<br>00-         |             |                   |      |      |      |              |      |      |      |      |      | v(put2)            |

| 20                  | ·           |                   |      |      |      |              |      |      |      |      |      | (V) : t(s)         |

| ε 10<br>0.0         |             |                   |      |      |      |              |      |      |      |      |      | (Dud)              |

| -1.0-               | 1<br>50n 10 | 1 150<br>1011 150 | 2101 | 2501 | 300h | 350n<br>t(¢) | 40(n | 45ûn | 500n | 55ûn | 600n | 681n               |

In this paper, we demonstrated the design of different ternary logic circuits based on QDGFETs. Less power dissipation was observed in the QDGFET-based ternary logic circuits than the other. The improved performance of the QDGFET-based ternary logic circuits was because of the fast resonant tunneling mechanism of the charge carriers from the inversion channel to the different layers of quantum dots in the gate region. We also did the comparative analysis of number of circuit elements required with QDGFET and CNTFET based circuit, which shows QDGFET based circuits requires less amount of circuit element compared with CNTFET. There will be uniform noise margin of the designed ternary logic circuits because of the less charge leakage between the quantum dots in the gate region of the QDGFET. This paper showed the improved performance of the ternary logic circuits based on the QDGFET because of the tunneling mechanism and the cladded dots in the gate region. The improved performance of the different QDGFET-based ternary logic circuits will make QDGFET a promising circuit element in MVL circuits in the future.

## REFERENCES

- J.T. Butler, Multiple-Valued logic in VLSI, IEEE Computer Society Press Technology Series, Los Alamitos, CA, 1991.

- [2]. E. Dubrova, "Multiple-valued logic in VLSI: challenges and opportunities," in 17<sup>th</sup> NORCHIP Conference, 1999, pp. 340-9.

- [3]. H. C. Lin, "Resonant tunneling diodes for multi-valued digital applications," in Proc. 24th IEEE Int. Symp. Multiple-Valued Logic, May 1994, pp. 188–195.

- [4]. A. Forster, "Resonant tunneling diodes: The effect of structural properties on their performance," in Advances in Solid State Physics, vol. 33.New York: Springer-Verlag, 1994, pp. 37–62.

- [5]. A. C. Seabaugh, W. R. Frensley, J. N. Randall, M. A. Reed, D. L. Farrington, and R. J. Matyi, "Pseudomorphic bipolar quantum resonant tunneling transistor," *IEEE Trans. Electron Devices*, vol. 36, no. 10, pp.2328–2334, Oct. 1989.

- [6]. J. Stock, J. Malindretos, K. M. Indlekofer, M. Pottgens, A. Forster, and H. Luth, "A vertical resonant tunneling transistor for

Copyright to IJAREEIE

An ISO 3297: 2007 Certified Organization

Vol. 3, Special Issue 3, April 2014

International Conference on Signal Processing, Embedded System and Communication Technologies and their applications for Sustainable and Renewable Energy (ICSECSRE '14)

Organized by

#### Department of ECE, Aarupadai Veedu Institute of Technology, Vinayaka Missions University,

#### Paiyanoor-603 104, Tamil Nadu, India

applicationin digital logic circuits," *IEEE Trans. Electron Devices*, vol. 48, no. 6, pp. 1028–1032, Jun. 2001.

- [7]. F. Capasso and R. A. Kiehl, "Resonant tunneling transistor with quantum well base and high-energy injection: A new negative differentialresistance device," *J. Appl. Phys.*, vol. 58, no. 3, pp. 1366–1368, Aug.1985.

- [8]. A. A. Ketterson, J.-W. Seo, M. H. Tong, K. L. Nummila, J. J. Morikuni, K.-Y. Cheng, S.-M. Kang, and I. Adesida, "A MODFET-based optoelectronic integrated circuit receiver for optical interconnects," *IEEE Trans.Electron Devices*, vol. 40, no. 8, pp. 1406–1416, Aug. 1993.

- [9]. S. M. S. Imtiaz and S. M. El-Ghazaly, "Performance of MODFET and MESFET: A comparative study including equivalent circuits using combined electromagnetic and solid-state simulator," *IEEE Trans. Microw.Theory Tech.*, vol. 46, no. 7, pp. 923–931, Jul. 1998.

- [10]. H. Rohdin, A. Nagy, V. Robbins, C.-Y. Su, A. S. Wakita, J. Seeger, T. Hwang, P. Chye, P. E. Gregory, S. R. Bahl, F. G. Kellert, L. G.Studebaker, D. C. D'Avanzo, and S. Johnsen, "0.1-μm gate-length AlInAs/GalAs/GaAs MODFET MMIC process for applications inhigh-speed wireless communications," *Hewlett Packard J.*, no. 4, pp.1–26, Feb. 1998.

- [11]. J.-H. Tsai, "High-performance AlInAs/GaInAsδ-doped HEMT with negative differential resistance switch for logic application," *Solid-State Electron.*, vol. 48, no. 1, pp. 81–85, Jan. 2004.

- [12]. W. Kruppa and J. B. Boos, "Observation of DC and microwave negative differential resistance in InAlAs/InGaAS/InP HEMTs," *Electron. Lett.*,vol. 28, no. 3, pp. 267–269, Jan. 1992.

- [13]. E. M. Chumbes, A. T. Schremer, J. A. Smart, Y. Wang, N. C. MacDonald, D. Hogue, James J. Komiak, S. J. Lichwalla, R. E. Leoni, and J.R. Shealy, "AlGaN/GaN high electron mobility transistors on Si(111) substrates," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 1–7, Mar.2001

- [14]. F. C. Jain, E. Heller, S. Karmakar, and J. Chandy, "Device and circuit modeling using novel 3-state quantum dot gate FETs," in *Proc. Int. Semicond. Device Res. Symp.*, Dec. 2007, pp. 1–2.

- [15]. J. A. Chandy and F. C. Jain, "Multiple valued logic using 3-state quantum dot gate FETs," in *Proc. 38th Int. Symp. Multiple Valued Logic*,2008, pp. 186–190.

- [16]. A. Raychowdhury and K. Roy, "A novel multiple-valued logic design using ballistic carbon nanotube FETs," in *Proc. 34th Int. Symp. MultipleValued Logic*, May 2004, pp. 14–19.

- [17]. P. C. Balla and A. Antoniou, "Low power dissipation MOS ternary logic family," *IEEE J. Solid-State Circuits*, vol. 19, no. 5, pp. 739–749, Oct.1984.

- [18]. S. Lin, Y.-B. Kim, and F. Lombardi, "CNTFET-based design of ternary logic gates and arithmatic circuits," *IEEE Trans. Nanotechnol.*, vol. 10, no. 2, pp. 217–225, Mar. 2001.

- [19]. W. Gang, C. Li, and L. Qin, "Ternary logic circuit design based on single electron transistors," J. Semicond., vol. 30, no. 2, pp. 025011–025015, Feb. 2009.

- [20]. F.C. Jain, E. Heller, S. Karmakar, and J. Chandy, "Device and Circuit Modeling using novel 3-state quantum DOT gate FETs" in Proceedings of International Semiconductor Device Research Symposium, Dec. 2007.

- [21]. F.C. Jain, E. Suarez, M. Gogna, F. Al-Amoody, D. Butkiewicus, R. Hohner, T. Liaskas, S. Karmakar, P.Y. Chan, B. Miller, J. Chandy and E. Heller, "Novel Quantum Dot Gate FETs and Nonvolatile Memories Using Lattice-Matched II-VI Gate Insulators", Journal of ELECTRONIC MATERIALS, Vol. 38, No. 8, 2009: 1574-8

- [22]. Tiwari S, Rana F, Chan K, Hanafi H, Chan W, and Buchanan D, Proc. IEDM 1995: pp. 521–524.

- [23]. Hinton HS, An introduction to photonic switching fabrics, Plenum, 1993.

- [24]. Yusa G and Sakaki H, Appl. Phys. Lett., 1997; 70, pp. 345–7[25]. Rack A, Wetzler R, Wacker A, and Scholl E, Proc. International

- Conference on the Physics of Semiconductors, 2002.

## BIOGRAPHY

**R.Rajith,**received his M.E. degree in VLSI Design at S.M.K Fomra institute of technology Chennai and he received B.E degree in Electronics and Communication engineering at Anand Institute of Higher Technologyunder Anna university, Chennai. Currently

working as Asst.Prof at S.M.K Fomra institute of technology Chennai. Area of interest is Image Processing and VLSI design.

SelvaPrabhu.S has received B.E Degree in Electronics and Communication Engineering, from Dr. M.G.R.. Educational And Research Institute. Presently pursuing M.E Degree in VLSI design at SMKFIT, Chennai. He has attended many conference and published many journals. Area of

interest are VLSI Design and digital electronics

Copyright to IJAREEIE