> (An ISO 3297: 2007 Certified Organization) Vol. 2, Special Issue 1, December 2013

# Design, Theoretical Modeling, Simulation and Validation of a Push-Pull DC-DC Converter

Siji Das<sup>1</sup>, Mrs.Jisha Kuruvilla<sup>2</sup>, Dr. Babu Paul<sup>3</sup>

M-Tech scholar, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India<sup>1</sup>

Asst. Professor, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India<sup>2</sup>

Associate Professor, Dept. of EEE, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India<sup>3</sup>

**Abstract**: This thesis aims at end to end design of a push-pull dc-dc converter with analog PWM controller. The pushpull converter circuitry consist of a power transfer stage with an appropriate switching device. Rectifier and filter circuits are used for filtering and smoothening of the output dc voltage. The switch duty ratio is controlled by means of a PWM controller chip. To improve the system stability and to obtain desired bandwidth compensation circuit is incorporated. EMI filters (both common mode and differential mode) are used to avoid unwanted signals in the circuit. The complete circuit is modelled and simulated to check the adequacy of the design. Circuit modelling and simulation is carried out by I-CAP4 simulation package.

Keywords: dc-dc converter, PWM controller, compensators, EMI filters, I-CAP4

#### I. INTRODUCTION

A dc-dc converter [1] is an electrical device that converts an unregulated dc input voltage into a well regulated output, typically within awell-defined tolerance level. The converter circuitry may be of isolated or non-isolated depending on the input and the output requirements. The circuit will usually consist of a power transfer stage with appropriate switching devices along with necessary input and output filters, feedback circuit, PWM controllers and compensators[2]. An increase of the system frequency [3] causes a considerable reduction in both size and cost of the associated components.

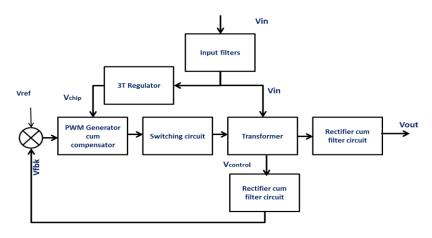

The thesis work aims at developing a complete converter circuitry that operates at high frequency. The basic block diagram of the proposed dc-dc converter is shown in fig.1.

Fig.1.DC-DC Converter Block Diagram

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Special Issue 1, December 2013

The converter circuitry was implemented using a push pull converter topology. This topology provides better input output isolation for the circuit at reduced cost. Also this arrangement can meet the requirement of multiple outputs whenever required. Buck & Boost converters do not have isolation and power limit is <100W. Fly back converter & forward converter recommended operating power is <150W and switching transformer core size to be larger by a factor of 2 in comparison with push-pull. Half bridge recommended power is 100-500W but the peak current through the switch at the same power is double that of push-pull. Also the no. of parts are higher compared to push-pull. Full bridge is meant for very high power and no. of parts are high. Hence push-pull topology is selected.

The main advantages of the proposed circuit are that the input EMI filters[4] incorporated into the circuit provide it better isolation from common and differential mode noises from outside interferences, compensation circuitry incorporated to the PWM generator improve the system stability by avoiding feedback loop oscillations. These advantages make the circuit useful for a wide range of applications including space shuttles, solar panels etc.

The developed circuitry has been simulated by using ICAP-4[5] circuit simulation package to check the accuracy of the design and the results have been studied. The simulation results are validated by conducting experimental results.

#### II. DESCRIPTION OF DC-DC CONVERTER SWITCHING SYSTEM

The switching circuit for the dc-dc converter consist mainly of a fast acting Push-Pull switching transformer that will change the supply voltage level to a different output voltage level as per the requirement. It consists of a transformer T1 with multiple secondary's. Each secondary delivers a pair of  $180^{\circ}$  out-of-phase square-wave power pulses whose amplitude is fixed by the input voltage and the number of primary and secondary turns. The pulse widths for all secondaries are identical, as determined by the control circuit and the negative-feedback loop around the *master* output. Transistor base drives at turn "on" are sufficient to bring theswitched end of each half primary down to Vce(sat), typically about 1 V, over the full specified current range. Hence as each transistorturns "on," it applies a square-voltage pulse to its half primary ofmagnitude( $V_{dc} - 1$ ). On the secondary side of the transformer, there will be flat-topped square waves of amplitude

$$\left(\frac{V_{dc}-1}{N_p}-V_d\right)$$

with a duration  $T_o$ , where  $V_d$  is an output rectifier forward drop, taken as 1 V for a

conventional fast-recovery diode, and 0.5 V for a Schottky diode. The output pulses at the rectifier cathodes have a duty cycle of 2T on/T because there are two pulses per period.

Thus the waveforms at the inputs to the LC filters are very much like that at the input to the buck regulator LC filterof Figure 1, which has a flat-topped amplitude and adjustable width. The LC filters provide a DC output that is the average of the square wave voltage at the input of the filter. The analysis of the inductor and capacitor functions proceeds exactly as for the buck regulator, and the method of calculating their magnitudes is exactly the same as follows. The DC or average voltage at the Vmoutput in Figure 2 will be

$$V_m = \left[ (V_{dc} - 1) \left( \frac{N_s}{N_p} \right) - V_d \right] \frac{2T_{on}}{T}$$

(1)

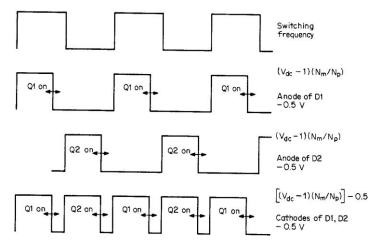

The waveforms at the Vmoutput rectifiers are shown in Figure 2.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Special Issue 1, December 2013

Fig.2.Voltage waveforms (Nm) at the secondary winding.

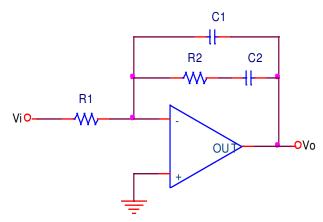

#### **III. PWM GENERATOR CUM COMPENSATOR**

The PWM generators is responsible for controlling the switch turn on and turn off so as to maintain the output within the prescribed tolerance level. Usually the circuit are with negative feedback loop and thus provides negative feedback and a stable output voltage at low frequencies. Within the loop, however, there are low-level noise voltages and voltage transients possible, which have a wide spectrum of sinusoidal Fourier components. If one of these Fourier components has a loop gain of 1 and a phase shift of a further 180° (the first 180 being provided by the negative feedback connection), the total phase shift will be 360°. Then the feedback signal will be in phase with the original input, resulting in positive rather than negative feedback, which will result in oscillation. The compensation circuitry incorporated into the system is used to avoid the feedback loop oscillations. The compensation circuit will increase the system stability margin and thus improves system stability and reduces the feedback loop oscillations. But eventually the system response timings will also increase.

The compensator circuitry was designed by analysing the system open loop response. The system transfer function is obtained as below:

Pulse width modulator gain, (2)

$G_{PWM}(s) = \frac{1}{V_{pp}}$  $G_{tr} = \frac{V_O}{V_{IN}} = \frac{N_S}{N_p}$ Transformer gain,

$$G_{in} = \left(\frac{(1+R_dC_d.s)}{s^3.L.C.C_d.R_d+s^2.L.(C+C_d))+R_d.C_d.s+1}\right)$$

(4)

$$O.L.T.F = \frac{V_{dc}}{V_{pp}} \left(\frac{N_s}{N_p}\right) \left(\frac{(1+R_dC_d.s)}{s^3.L.C.C_d.R_d+s^2.L.(C+C_d))+R_d.C_d.s+1}\right)$$

(5)

(3)

### (An ISO 3297: 2007 Certified Organization) Vol. 2, Special Issue 1, December 2013

Fig.3.Type 2 compensator

#### IV. INPUT FILTERS

DC-DC converters can generate and/or be affected byEMI. Sources are everywhere and include ac motors, fluorescent bulbs/ballasts, light dimmers, microwaveovens, microprocessors, computers, and switch-mode power supplies. Within switch-mode power supplies, a high dc voltage is chopped orswitched at a high frequency that can range from 50 kHz to 1 MHz. This high-speed switching process isintrinsic to switch-mode power supplies and provides its improved efficiency and reduced size when compared to linear power supplies. However, as a side effect, this switching generates unwanted EMI. Infact, most conducted EMI within switch-mode power supplies originates from the main switching MOSFETs, transistors, and output rectifiers.

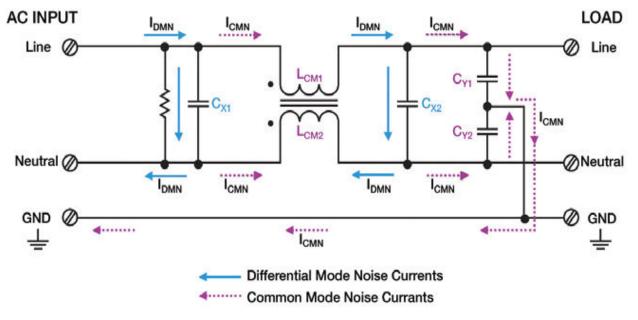

Conducted EMI is divided into two main types: Common-mode noise (CMN) and differential-mode noise (DMN). CMN, a.k.a. asymmetrical noise or line-to-ground noise, exists on both sides of the ac input (line and neutral), in-phase with itself relative to ground. The CMN current flows in the same direction on both power conductors and returns via the ground conductor. CMN can be suppressed by the use of inductors within an EMI filter that are placed in series with each power line and by Y-capacitors that are connected from both power line conductors to ground.

CMN is suppressed by using dual-wound toroid type inductors (LCM1 and LCM2). These inductors are wound on a single core in such a way that they present a high impedance to the in-phase common-mode noise on each ac conductor. In addition, the Y-capacitors (CY1 and CY2) shunt or bypass the high-frequency common mode noise to ground.

DMN on each ac conductor is suppressed by the two X-capacitors (CX1 and CX2), which tend to neutralize the outof-phase high-frequency DMN that exists between the ac power line and neutral conductors. The input resistor discharges these capacitors when the power is turned off.

(An ISO 3297: 2007 Certified Organization)

Fig.4.EMI filter suppressing common mode and differential mode noises.

### V. SIMULATION RESULTS

The designed circuit was simulated using I-CAP4 circuit simulation package and the results are studied. The design circuit specifications are given in table.

| CIRCUIT SPECIFICATIONS |           |  |

|------------------------|-----------|--|

| Parameter              | Value     |  |

| Input voltage          | 26-32V dc |  |

| Output voltage         | 160V      |  |

| Switching frequency    | 100KHz    |  |

| Efficiency             | 80%       |  |

| Maximum duty cycle     | .85       |  |

TABLE I CIRCUIT SPECIFICATIONS

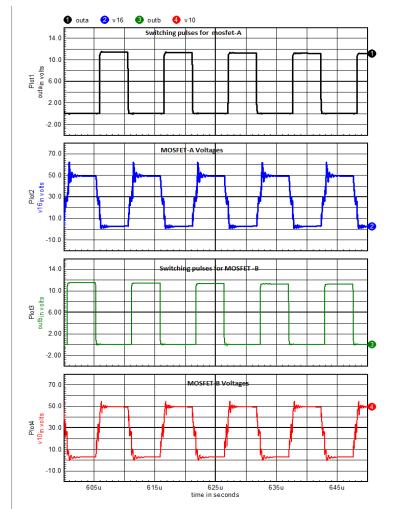

A. Results for 26V input

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Special Issue 1, December 2013

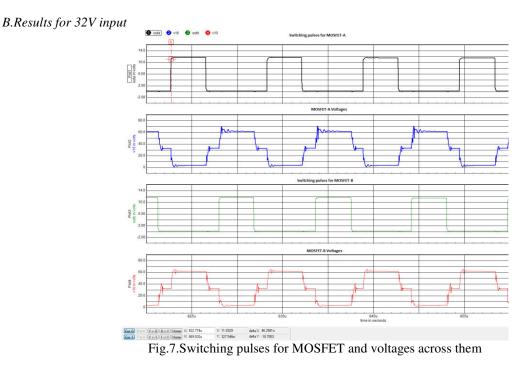

Fig.5.Switching pulses for the MOSFET switches and voltage across them.

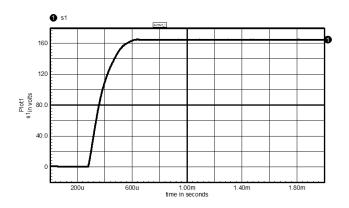

Fig.6.Output voltage for 26V input

(An ISO 3297: 2007 Certified Organization)

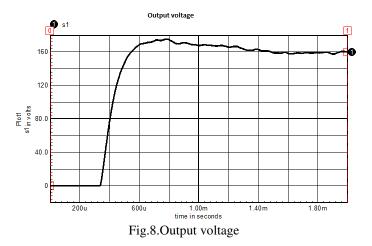

The results obtained after simulation is summarised in the table.2.

| TABLE II                   |

|----------------------------|

| SIMULATION RESULTS SUMMARY |

| Parameter      | 26V input | 32V input |

|----------------|-----------|-----------|

| Output voltage | 162V      | 160V      |

| Duty cycle     | 70%       | 90%       |

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Special Issue 1, December 2013

### VI. EXPERIMENTAL RESULTS

The circuit was validated by conducting experimental setup. The circuit was set up on a prototype chip and the input voltage is varied within prescribed limits. The result obtained shows a close match with the simulation results.

Fig.9.Results for 26V input

Fig.10.Results for 28.5V input

(An ISO 3297: 2007 Certified Organization) Vol. 2, Special Issue 1, December 2013

#

#### Fig.11.Results for 32V input

#### VII. CONCLUSION

In this paper the complete design of a high frequency DC-DC converter has been developed using push pull topology. EMI filters incorporated into the system make it isolated from the common mode and differential mode noises. Also addition of compensation circuitry improves the system stability. The simulation results have shown that the system the system can well regulate its output within a prescribed tolerance under the specified input supply variations. The results are then validated by conducting experimental setup.

#### REFERENCES

- [1] Julian Yan Zhu and Lehman B., 2005.Control loop design for two-stage dc-dc converters with low voltage/high current output.IEEE Trans. on Power Electronics, Vol. 20, No. 1.

- [2] Kittipeerachon, K.; Fac. of Eng., King Mongkut"s Inst. of Technol., Bangkok, Thailand; Bunlaksananusorn, C.Feedback compensation design for switched mode power supplies with a right-half plane (RHP) zero, Power Electronics, Machines and Drives, 2004. (PEMD 2004). Second International Conference on (Conf. Publ. No. 498) (Volume:1).

- [3] Juan M. Rivas, David Jackson, Olivia Leitermann, Anthony D. Sagneri, YehuiHan, David J. Perreault, Design Considerations for Very High Frequencydc-dc Converters, 37th IEEE Power Electronics Specialists Conference / June 18 - 22, 2006, Jeju, Korea.

- [4] D.C. Hamill "An Efficient Active Ripple Filter for Use in DC-DC Conversion," IEEE Transactions on Aerospace and Electronic Systems, Vol. 32, No. 3, July 1996, pp. 1077-1084.

- [5] www.intusoft.com/models

- [6] Switching power supply design by Abraham.j.Pressman,KeithBillings,TaylorMorey,Third edition.

- [7] Domingo.A.RuizCabarello,student member, IEEE, and Ivo Barbi,senior member, IEEE, *A New Fly-Back Current fed Push-Pull DC-DC Converter*, IEEE transactions on power electronics, VOL 14, No.6., November 1999.