# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

# Multilevel Inverter for Induction Motor Drives Using Reversing Voltage Topology

P.Himabindu<sup>1</sup>, S.Mallikarjunaiah<sup>2</sup>

PG Scholar, Department of EEE, Chadalawada Ramannama Engineering College, Tirupati, A.P, India<sup>1</sup> Professor, Department of EEE, Chadalawada Ramannama Engineering College, Tirupati, A.P, India<sup>2</sup>

**ABSTRACT:** In this paper, a novel topology called Reversing Voltage is implemented to improve multilevel performance by compensating the disadvantages in neutral point- clamped (NPC), flying capacitors (capacitor clamped), cascaded H-bridge (multi-cell) topologies. This new power converter topology requires fewer components compared to available multi-level inverters (especially in higher-levels) and requires less carrier signals for PWM implementation. Also, it requires less number of switches which reduces the number of gate drive circuits. Therefore, the overall cost and complexity are greatly reduced particularly for higher output voltage levels. The simulation is to be done for 1-phase five level inverter for R-L, 1-phase Induction Motor loads and 3-phase five level inverter for 3-phase Induction Motor load and also Seven level inverter is to be simulated for resistive and inductive loads. The simulation for the above topology is carried out in MATLAB/SIMULINK environment.

**KEYWORDS:** Reversing Voltage topology, neutral point- clamped, flying capacitors, cascaded H-bridge, PWM technique.

## **I.INTRODUCTION**

Multi-level inverter technology has emerged recently as a very important alternative in the area of medium-voltage high-power energy control. Their performance is highly superior to that of conventional two-level inverters due to higher number of dc voltage sources, lower EMI, necessity of semiconductor power devices with less blocking voltage, lower percentage THD in output voltage and less stress on insulation. However, it has some disadvantages as complicated PWM controlling technique, increased number of components, complex power bus structure in approximate topologies, and voltage balancing problem at neutral point. Various topologies are used for the multi-level inverters. Among this the most commonly used topologies are neutral point- clamped (NPC), flying capacitors (capacitor clamped), cascaded H-bridge (multi-cell) and dual inverter fed open-ended winding induction motor (IM) structure.

# **II.REVERSING VOLTAGE TOPOLOGY**

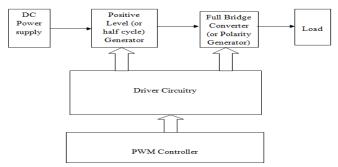

This topology is a hybrid multilevel topology which separates the output voltage into two parts. One part is called level generation part and is responsible for level generating in positive polarity. This part needs high-frequency switches to generate the required levels. The switches in this part must have high-switching-frequency capability. The additional part is called polarity generation part and is responsible for generating the polarity of the output voltage, which is the low-frequency part functioning at line frequency. The topology combines the two parts (high frequency and low frequency) to generate the multilevel voltage output. In order to generate a complete multilevel output, the positive levels are produced by the high-frequency part (level generation), and then, this part is served to a full-bridge inverter (polarity generation), which will generate the necessary polarity for the output. This will eradicate many of the semiconductor switches which were responsible to generate the output voltage levels in positive and negative polarities. The block diagram of multi-level inverter using Reversing Voltage topology is shown in Figure 1.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

## Vol. 3, Issue 12, December 2014

Fig 1.Block diagram of multi-level inverter using reversing voltage topology

## III. APPLICATION IN FIVE LEVEL INVERTER

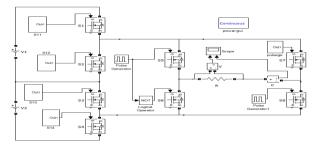

Figure 2 shows the simulation model of a single phase five level inverter of RV-Topology for R –Load in simulink model. From this simulink model the output voltage and current waveforms are observed for R-Load. The principal idea of this topology as a multilevel inverter is that the left stage in generates the required output levels (without polarity) and the right circuit (full bridge converter) decides about the polarity of the output voltage. This part, which is named polarity generation, transfers the required output level to the output with the same direction or opposite direction according to the required output polarity. It reverses the voltage direction when the voltage polarity requires to be changed for negative polarity that is during negative half cycle of the output voltage.

Fig 2.Model of a single phase five level inverter of RV-topology for R –Load

## IV.APPLICATION IN SEVEN LEVEL INVERTER

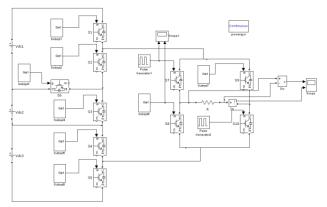

Figure 3 shows the simulation model of a single phase seven level inverter of RV-Topology for R –Load in simulink model. From this simulink model the output voltage and current waveforms are observed for R-Load.

Fig 3.Model of a single phase seven level of RV-topology for R-load

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

# Vol. 3, Issue 12, December 2014

# **V.SIMULATION RESULTS**

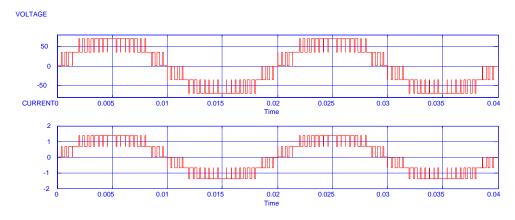

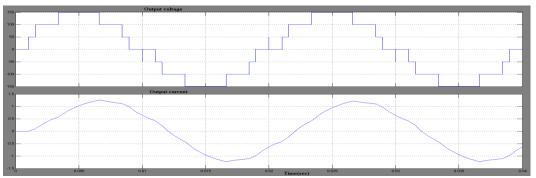

In this part the simulation results of single phase five level inverter for R and RL loads are shown, simulation results for three phase five level inverter for R and Induction Motor loads are show and also simulation results of single phase seven level inverter for R and RL loads are shown.

Fig 4.Output voltage and current waveforms of Single phase five level inverter for R-load

Another advantage of this topology is that it requires fewer components in comparison to conventional multi-level inverters. It also requires less high frequency switches.

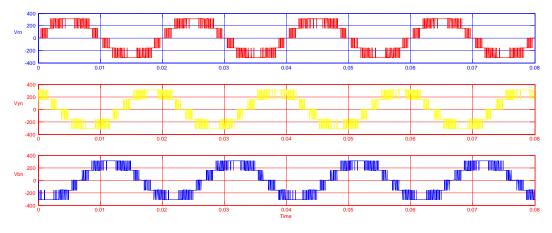

Fig 6.Output voltage waveforms of 3-phase 5-level inverter for R-load

In the following output waveforms shows the results regarding output voltage ,output current and speed –Torque characteristics of a 3-phase induction motor by using reverse voltage topology in 5-level inverter.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

# Vol. 3, Issue 12, December 2014

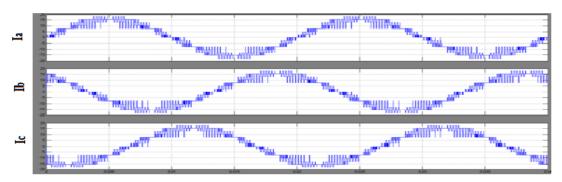

Fig 7.Output line currents of 3-phase 5-level inverter for induction motor load

Fig 8.Speed and Torque characteristics with respect to time

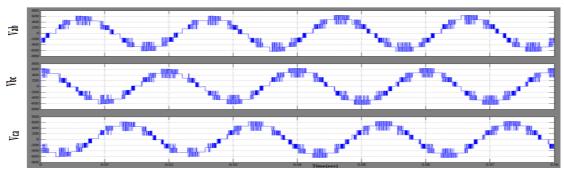

Fig 9.Output line voltages across induction motor load

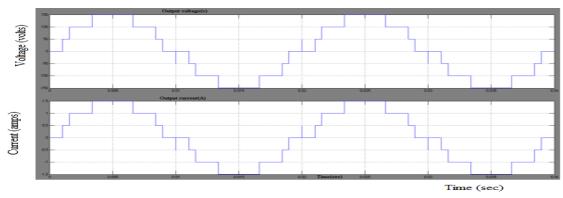

The below waveforms represents the output waveforms of R-load and RL-load for 7-level inverter by using reverse voltage topology.

Fig 10.Output voltage and output current waveforms for R-load

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 12, December 2014

Fig 11.Output voltage and output current waveforms for RL – load

## **VI.CONCLUSIONS**

Matlab-Simulink models of a single phase five level and seven level inverters with RV topology are developed and output voltage and current waveforms are observed for both R and RL loads. As well three phase five level inverter is developed and output voltage, output current waveforms are detected for R-load and induction motor loads. The switching pulses are resulting based on phase disposition of sinusoidal pulse width modulation. In phase temper sinusoidal Pulse Width Modulation, all the carrier waveforms are in phase. In this topology, the amount of pulse carriers required is half of the pulse carriers that required for conventional topologies.

#### VII.SCOPE FOR THE FUTURE WORK

The reversing voltage topology can be implemented for higher voltage levels. It can be extended for nine level and eleven level inverters. In order to cover strict voltage harmonic standards in a static compensator this inverter topology can be used for such applications as it requires fewer components.

## REFERENCES

- [1] EhsanNajafi; and Abdul Halim Mohamed Yatim. "Design and Implementation of a New Multilevel Inverter Topology." IEEE Trans. Ind. Electronics.vol-59, no.11, NOVEMBER 2012.

- [2] E.Najafi, A.H.M.Yatim and A.S. Samosir. "A new topology-reversing voltage (RV) for multi-level inverters." 2nd International conference on power and energy (PECon 08),pp 604-608, December 2008 Malaysia

- [3] A. Nabe, I. Takahashi and H. Akagi. "A new neutral point clamped PWM inverter." IEEE Trans. Ind. Applicat. vol. 1A-17, pp 518-523, sep./oct. 1981.

- [4] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," IEEE Trans. Ind. Appl., vol. 35, no. 1, pp. 36–44, Jan./Feb. 1999.

- [5] Jose Rodriguez, Jih-Sheng Lai and Fang ZhengPeng. "Multilevel Inverters: A survey of topologies, controls and applications." IEEE Trans. Ind. Electronics.vol-49 no.4 pp 724-738, Aug. 2002.

- [6] Liu zhiqiang , Lu hongli ; Hexu Sun and Wang hongwen ; "A Simple Scheme Based on Space-Vector Pulse-width Modulation for Three-phase Rectifier." IEEE Trans. Ind. Electronics. pp, 0-7803-7 156-91021 Aug. 2002

- [7] B.R. Lin and C.H. Huang.; Analysis and implementation of a single-phase capacitor-clamped inverter with simple structure 2004 IEE Proc.-Electr. Power Appl., Vol. 151, No. 5, September 2004

- [8] K. Jang-Hwan, S.-K.Sul, and P. N. Enjeti, "A carrier-based PWM method with optimal switching sequence for a multilevel four-leg voltagesource inverter," IEEE Trans. Ind. Appl., vol. 44, no. 4, pp. 1239–1248, Jul./Aug. 2008.

- [9] C.Y.Leong; N-A. Parker-Allotey, R.A. McMahon; "Loss Comparison between an SPWM and Harmonic Elimination Excited Small, (<1kW) Induction Motor Drive using Pspice Simulation and Calorimetry. IEEE Trans. Ind.Electronics. pp 978-1-4244-2279-1/08, Aug. 2008