(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 2, February 2014

# Parametric variation analysis of CUK converter for constant voltage applications

Rheesabh Dwivedi<sup>1</sup>, Vinay Kumar Dwivedi<sup>2</sup>, Rahul Sharma<sup>3</sup>

Assistant Professor, Department of Electrical Engineering, Teerthanker Mahaveer University, Moradabad, Uttar Pradesh, India<sup>1,2</sup>

Lecturer, Department of Electrical Engineering, Teerthanker Mahaveer University, Moradabad,

Uttar Pradesh, India<sup>3</sup>

Abstract: This paper presents an optimized controller for non-isolated DC-DC CUK converter for constant voltage applications. CUK converter has inverted voltage polarity at the output, however, it operates on the principle of capacitive energy transfer and uses inductors on both sides of the switch to reduce current ripple. MOSFETs are used as a switching device in low power and high frequency switching applications. It may be noted that, as the turn-on and turn-off time of MOSFETs are lower as compared to other switching devices, which reduces the switching losses. High frequency operation of MOSFET reduced size of filters components. These converters are now being used for various applications, such as Switched Mode Power Supply (SMPS) etc. The paper attempts to present parametric variation analysis of buck-boost converters for constant voltage output.

Keywords: CUK Converter, Duty cycle, PI Controller, PWM

## I. INTRODUCTION

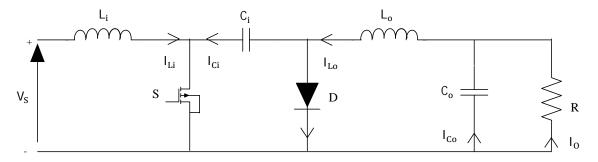

The basic non-isolated Cuk converter shown in Fig.1. It is one of the best basic DC-DC converters because its output voltage is negative and the output voltage may be higher or lower than the input voltage. It is widely used in electrical power system, communication, instruments and meters etc. The advantage of the basic non isolated Cuk converter over the standard buck–boost converter is to provide regulated DC output voltage at higher efficiency and this also reduce ripple currents and reduced switching losses. The basic non isolated Cuk converter is a switching power supply with two inductors, two capacitors, a diode, and a transistor switch. The transfer capacitor  $C_i$  stores and transfers energy from the input to the output.

Fig. 1 Schematic diagram of non-isolated Cuk converter

## II. OPERATING MODES OF CUK CONVERTER

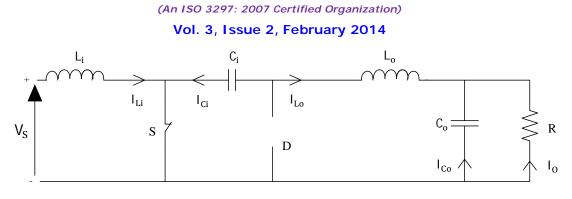

The converter circuit is divided into two parts as shown in fig.2 and fig.3. During mode 1, when transistor switch is closed then current through inductor  $L_i$  rises. At the same time the voltage of capacitor  $C_i$  reverse biases diode D and turns it off. The capacitor  $C_i$  discharges its energy to the circuit formed by  $C_i$ ,  $C_0$ ,  $L_0$  and the load.

Fig.2 Mode 1: Switch Closed

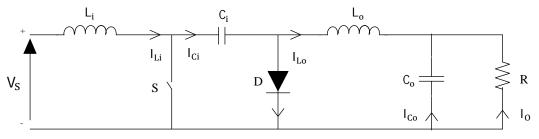

During mode 2, when the input voltage is turned on and switch S is open then diode D is forward biased and capacitor  $C_i$  is charged through  $L_i$ , D and the input supply  $V_S$ . The energy which is stored in the inductor  $L_0$  is transferred to the load. The diode D and the switch S provide a synchronous switching action.

Fig.3 Mode 2: Switch Open

The Cuk converter can step the voltage either up or down, depending on the duty cycle. The Cuk converter contain the series inductors at both input and output, hence it has much lower current ripple in both circuits. The average output voltage can be calculated in term of the switch duty cycle.

D = on time duration of switch/ total switching time period

Duty cycle =

$$-\frac{V_0}{V_S - V_0}$$

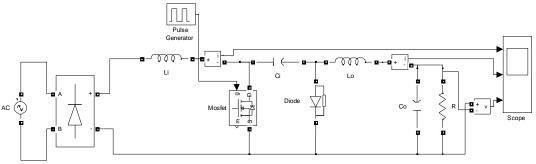

Output voltage  $(V_o) = -V_S \left[\frac{D}{1-D}\right]$  (Where the negative sign indicates voltage inversion) Control schematic of CUK converter output voltage is assumed to be 400V. A simple CUK converter model realize in MATLAB Simulink is shown in fig.5

Fig. 4 Simulink model of open loop non- isolated Cuk converter

Design parameter and equations for non-isolated Cuk converter:  $V_0 = DV_{in}/(1 - D)$   $L_i = DV_{in}/(\Delta I_{Li}) f_s$   $L_0 = V_0(1 - D)/(\Delta I_{L0}) f_s$ Copyright to IJAREEIE www.ijam

www.ijareeie.com

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 2, February 2014

$\begin{array}{l} C_{i} = D/\{(Rf_{s})(\Delta V_{Ci}/V_{0})\}\\ C_{0} = (1-D)/\{(BL_{0}f_{s}^{-2})(\Delta V_{Co}/V_{o})\}\\ \text{Where}\\ f_{s} = \text{switching frequency}\\ \Delta I_{Li} = \text{peak to peak ripple current }I_{Li} \text{ (assuming 10% of }I_{Li})\\ \Delta I_{Lo} = \text{peak to peak ripple current }I_{Lo} \text{ (assuming 10% of }I_{Lo})\\ \Delta V_{Ci} = \text{ voltage ripple (assuming 5% of }V_{0})\\ D = \text{duty cycle}\\ \text{Calculated value of design variables are }D=0.562, L_{i}=54.47\times10^{-3}\text{ H}, L_{o}=70\times10^{-3}\text{ H}, C_{i}=1.125\times10^{-6}\text{ F} \text{ and }C_{o}=0.025\times10^{-6}\text{ F} \end{array}$

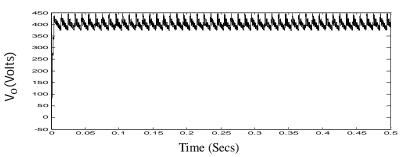

Fig.5 Open loop response of non-isolated Cuk converter

The results of open loop CUK converter is shown in fig.7, which depicts peak to peak ripple voltage ( $\Delta Vo$ ) is 54 Volt and maximum overshoot of 10%. Since the design equations assume constant input voltage and constant load under steady state conditions, the variation of input voltage shall result in fluctuation in output Therefore, a closed loop controller is required with optimized parameters to suit the constant voltage output as per requirement of load.

## III. CLOSED LOOP CUK CONVERTER

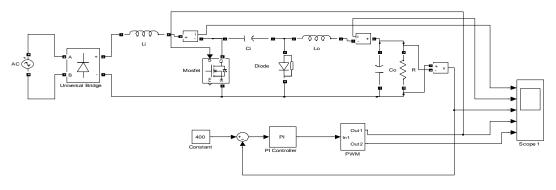

The Simulink Schematic of CUK converter with analog PI controller is shown in fig. 8

Fig. 6 Simulink model of closed loop Cuk converter

The output voltage is sensed  $V_{out}$  and compared with the input voltage  $V_{ref}$ . An error signal is produced which is processed through PI controller to generate a control voltage. The control voltage is used to feed to the PWM generator for control of switch. The PI controller has two parameters namely  $K_P$  and  $K_I$ .

PI controller has transfer function:  $C(s) = K_P + \frac{K_i}{s}$

Copyright to IJAREEIE

www.ijareeie.com

7110

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 2, February 2014

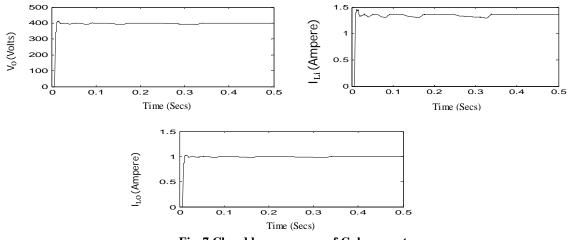

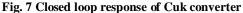

The results of closed loop CUK converter is shown in fig.9 which has maximum overshoot of 3.2%, settling time 0.0116 sec and rise time 0.0107 sec.

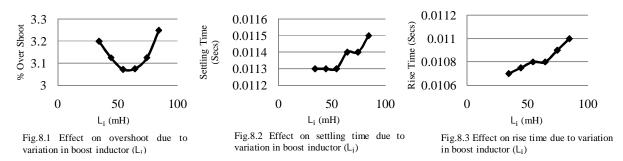

TABLE I AND FIG 8-10 SHOWS VARIATION OF PERFORMANCE PARAMETERS FOR VARIATION OF BOOST INDUCTOR (L<sub>i</sub>) VALUE IS VARIED.

| Li    |       | Voltage(V | <sub>0</sub> ) | (       | Current $(I_{Li})$ |      | Current (I <sub>Lo</sub> ) |          |         |

|-------|-------|-----------|----------------|---------|--------------------|------|----------------------------|----------|---------|

| (mH)  | O.S   | Settling  | Rise Time      | O.S (%) | Settling           | Rise | O.S (%)                    | Settling | Rise    |

|       | (%)   | Time      |                |         | Time               | Time |                            | Time     | Time    |

| 34.47 | 3.2   | 0.0113    | 0.0107         | 7.94    | 0.01               | 0.01 | 3.2                        | 0.0107   | 0.0107  |

| 44.47 | 3.125 | 0.0113    | 0.01075        | 7.4     | 0.01               | 0.01 | 3.1                        | 0.01073  | 0.0107  |

| 54.47 | 3.072 | 0.0113    | 0.0108         | 7.2     | 0.01               | 0.01 | 3                          | 0.0108   | 0.0108  |

| 64.47 | 3.075 | 0.0114    | 0.0108         | 7.46    | 0.01               | 0.01 | 3.07                       | 0.0109   | 0.01085 |

| 74.47 | 3.125 | 0.0114    | 0.0109         | 7.5     | 0.01               | 0.01 | 3.12                       | 0.0109   | 0.0109  |

| 84.47 | 3.25  | 0.0115    | 0.011          | 8.25    | 0.01               | 0.01 | 3.25                       | 0.011    | 0.011   |

Fig.8 Effect on output voltage (V<sub>0</sub>) due to variation in boost inductor (L<sub>i</sub>)

(An ISO 3297: 2007 Certified Organization)

## Vol. 3, Issue 2, February 2014

When the value of boost inductor  $(L_i)$  increases up to two times of the designed value then output voltage  $(V_0)$  overshoot, settling time and rise time continuously increases. If the value of boost inductor  $(L_i)$  decreases from its designed value then output voltage  $(V_0)$  overshoot increases continuously, settling time remains constant and rise time continuously decreases.

Fig.9 Effect on inductor current (IL<sub>i</sub>) due to variation in boost inductor (L<sub>i</sub>)

When the value of boost inductor  $(L_i)$  increases up to two times of the designed value then boost inductor current  $(I_{Li})$  overshoot continuously increases, settling time and rise time remains constant. If the value of boost inductor  $(L_i)$  decreases from its designed value then boost inductor current  $(I_{Li})$  overshoot continuously increases, settling time and rise time remains constant.

Fig.10 Effect on inductor current (IL<sub>0</sub>) due to variation in boost inductor (L<sub>i</sub>)

When the value of boost inductor  $(L_i)$  increases up to two times of the designed value then filter inductor current  $(I_{Lo})$  overshoot, settling time and rise time continuously increases. If the value of boost inductor  $(L_i)$  decreases from its designed value then filter inductor current  $(I_{Lo})$  overshoot increases continuously, settling time and rise time continuously decreases.

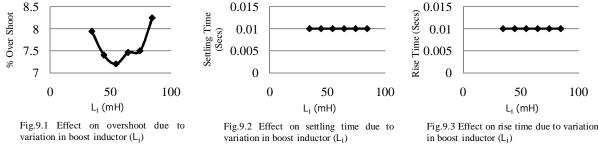

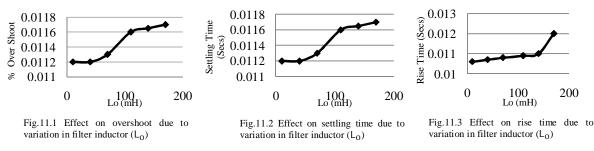

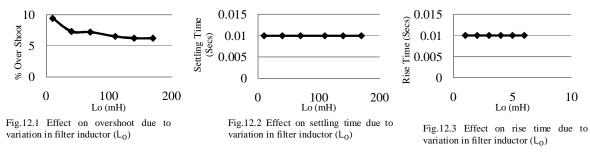

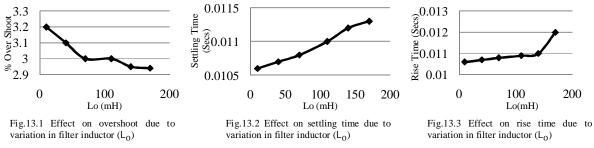

TABLE II AND FIG 11-13 SHOWS VARIATION OF PERFORMANCE PARAMETERS FOR VARIATION OF FILTER INDUCTOR ( $L_0$ ) VALUE IS VARIED.

| TABLE II RESULTS OF FILTER INDUCTOR (L <sub>0</sub> ) VARIATION. |                          |          |        |      |              |      |                            |          |        |  |  |

|------------------------------------------------------------------|--------------------------|----------|--------|------|--------------|------|----------------------------|----------|--------|--|--|

| L <sub>0</sub><br>(mH)                                           | Voltage(V <sub>0</sub> ) |          |        |      | Current (ILi | )    | Current (I <sub>Lo</sub> ) |          |        |  |  |

|                                                                  | O.S                      | Settling | Rise   | O.S  | Settling     | Rise | O.S                        | Settling | Rise   |  |  |

| (1111)                                                           | (%)                      | Time     | Time   | (%)  | Time         | Time | (%)                        | Time     | Time   |  |  |

| 10                                                               | 3.2                      | 0.0112   | 0.0106 | 9.4  | 0.01         | 0.01 | 3.2                        | 0.0106   | 0.0106 |  |  |

| 40                                                               | 3.125                    | 0.0112   | 0.0107 | 7.3  | 0.01         | 0.01 | 3.1                        | 0.0107   | 0.0107 |  |  |

| 70                                                               | 3.072                    | 0.0113   | 0.0108 | 7.2  | 0.01         | 0.01 | 3                          | 0.0108   | 0.0108 |  |  |

| 110                                                              | 3                        | 0.0115   | 0.0109 | 6.5  | 0.01         | 0.01 | 3                          | 0.011    | 0.0109 |  |  |

| 140                                                              | 2.95                     | 0.0116   | 0.011  | 6.22 | 0.01         | 0.01 | 2.95                       | 0.0112   | 0.011  |  |  |

| 170                                                              | 2.95                     | 0.0117   | 0.012  | 6.21 | 0.01         | 0.01 | 2.94                       | 0.0113   | 0.012  |  |  |

TABLE II RESULTS OF FILTER INDUCTOR (L<sub>0</sub>) VARIATION

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 2, February 2014

Fig.11 Effect on output voltage (V<sub>0</sub>) due to variation in filter inductor (L<sub>0</sub>)

When the values of ripple filter inductor  $(L_0)$  increases up to two times of the designed value then output voltage  $(V_0)$  overshoot decreases, settling time and rise time continuously increases. If the values of ripple filter inductor  $(L_0)$  decreases up to seven times from its designed value then output voltage  $(V_0)$  overshoot increases, settling time and rise time continuously decreases.

Fig.12 Effect on inductor current (IL<sub>i</sub>) due to variation in filter inductor (L<sub>0</sub>)

When the value of ripple filter inductor  $(L_0)$  increases up to two times of the designed value then boost inductor current  $(I_{Li})$  overshoot decreases, settling time and rise time remains constant. If the values of ripple filter inductor  $(L_0)$  decreases up to seven times from its designed value then boost inductor current  $(I_{Li})$  overshoot increases, settling time and rise time remains constant.

Fig.13 Effect on inductor current (IL<sub>0</sub>) due to variation in filter inductor (L<sub>0</sub>)

When the value of ripple filter inductor  $(L_0)$  increases up to two times of the designed value then filter inductor current  $(I_{L_0})$  overshoot decreases, settling time and rise time increases. If the values of ripple filter inductor  $(L_0)$  decreases up to seven times from its designed value then filter inductor current  $(I_{L_0})$  overshoot increases, settling time and rise time continuously decreases.

(An ISO 3297: 2007 Certified Organization)

## Vol. 3, Issue 2, February 2014

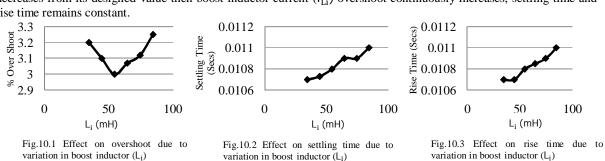

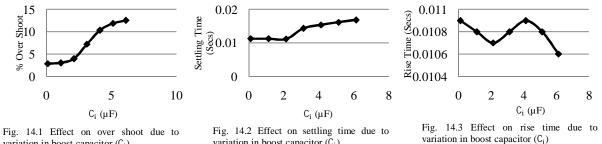

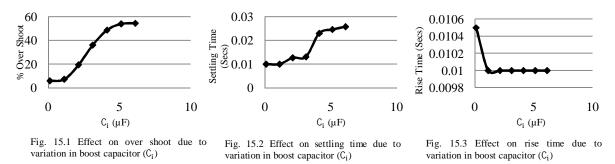

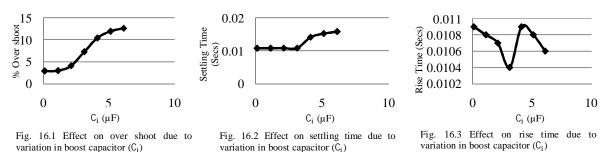

TABLE III AND FIG 14-16 SHOWS VARIATION OF PERFORMANCE PARAMETERS FOR VARIATION OF BOOST CAPACITOR (C<sub>i</sub>) VALUE IS VARIED.

| C <sub>i</sub> (µF) | Voltage(V <sub>o</sub> ) |                  |              |         | Current (I <sub>Li</sub> ) |              | Current (I <sub>Lo</sub> ) |                  |           |  |

|---------------------|--------------------------|------------------|--------------|---------|----------------------------|--------------|----------------------------|------------------|-----------|--|

|                     | O.S (%)                  | Settling<br>Time | Rise<br>Time | O.S (%) | Settling<br>Time           | Rise<br>Time | O.S (%)                    | Settling<br>Time | Rise Time |  |

| 0.1125              | 2.875                    | 0.0113           | 0.0109       | 5.93    | 0.01                       | 0.0105       | 2.9                        | 0.0108           | 0.0109    |  |

| 1.125               | 3.072                    | 0.0113           | 0.0108       | 7.2     | 0.01                       | 0.01         | 3                          | 0.0108           | 0.0108    |  |

| 2.125               | 4                        | 0.0112           | 0.0107       | 19.37   | 0.0127                     | 0.01         | 4.1                        | 0.01081          | 0.0107    |  |

| 3.125               | 7.25                     | 0.0144           | 0.0108       | 36.02   | 0.0131                     | 0.01         | 7.26                       | 0.01082          | 0.0104    |  |

| 4.125               | 10.38                    | 0.0154           | 0.0109       | 48.67   | 0.023                      | 0.01         | 10.4                       | 0.0141           | 0.0109    |  |

| 5.125               | 11.91                    | 0.0162           | 0.0108       | 53.9    | 0.0246                     | 0.01         | 11.91                      | 0.0152           | 0.0108    |  |

| 6.125               | 12.6                     | 0.0169           | 0.0106       | 54.41   | 0.0258                     | 0.01         | 12.6                       | 0.0158           | 0.0106    |  |

#### TABLE III RESULTS OF BOOST CAPACITOR (C<sub>i</sub>) VARIATION.

variation in boost capacitor (C<sub>i</sub>)

variation in boost capacitor  $(C_i)$

Fig.14 Effect on output voltage  $(V_0)$  due to variation in boost capacitor  $(C_i)$

When the value of boost capacitor ( $C_i$ ) increases up to six times of the designed value then output voltage ( $V_0$ ) overshoot and settling time increases and rise time decreases. If the values of boost capacitor (C<sub>i</sub>) decreases from the designed value then output voltage  $(V_0)$  overshoot decreases, settling time remains constant and rise time increases.

Fig.15 Effect on inductor current (IL<sub>i</sub>) due to variation in boost capacitor (C<sub>i</sub>)

When the value of boost capacitor ( $C_i$ ) increases up to six times of the designed value then boost inductor current ( $I_{Li}$ ) overshoot and settling time continuously increases and rise time remains constant. If the values of boost capacitor (C<sub>i</sub>) decreases from the designed value then boost inductor current (I<sub>Li</sub>) overshoot decreases, settling time remains constant and rise time increases.

(An ISO 3297: 2007 Certified Organization)

## Vol. 3, Issue 2, February 2014

Fig.16 Effect on inductor current (IL<sub>0</sub>) due to variation in boost capacitor (C<sub>i</sub>)

When the value of boost capacitor  $(C_i)$  increases up to six times of the designed value then filter inductor current  $(I_{Lo})$  overshoot and settling time continuously increases and rise time decreases. If the values of boost capacitor  $(C_i)$  decreases from the designed value then filter inductor current  $(I_{Lo})$  overshoot decreases, settling time remains constant and rise time increases.

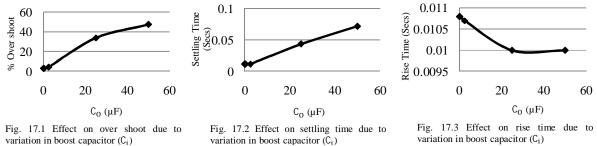

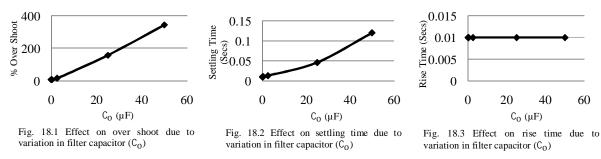

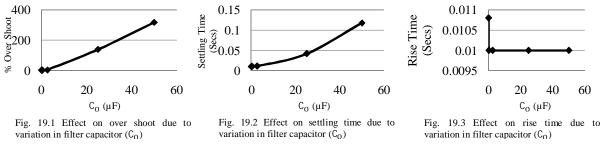

TABLE IV AND FIG 17-19 SHOWS VARIATION OF PERFORMANCE PARAMETERS FOR VARIATION OF FILTER CAPACITOR (C<sub>0</sub>) VALUE IS VARIED.

| C <sub>o</sub><br>(µF) | Voltage (V <sub>0</sub> ) |                  |           | Current (I <sub>Li</sub> ) |                  |              | Current (I <sub>Lo</sub> ) |                  |           |

|------------------------|---------------------------|------------------|-----------|----------------------------|------------------|--------------|----------------------------|------------------|-----------|

|                        | O.S<br>(%)                | Settling<br>Time | Rise Time | O.S<br>(%)                 | Settling<br>Time | Rise<br>Time | O.S<br>(%)                 | Settling<br>Time | Rise Time |

| 0.00025                | 3.07                      | 0.0113           | 0.0108    | 6.88                       | 0.01             | 0.01         | 3                          | 0.0107           | 0.0108    |

| 0.0025                 | 3.071                     | 0.0113           | 0.0108    | 6.9                        | 0.01             | 0.01         | 3                          | 0.0108           | 0.0108    |

| 0.025                  | 3.072                     | 0.0113           | 0.0108    | 7.2                        | 0.0102           | 0.01         | 3                          | 0.0108           | 0.0108    |

| 0.25                   | 3.072                     | 0.0113           | 0.0108    | 7.79                       | 0.0105           | 0.01         | 3.1                        | 0.01081          | 0.01      |

| 2.5                    | 4.5                       | 0.0115           | 0.0107    | 16.8                       | 0.013            | 0.01         | 6.6                        | 0.0118           | 0.01      |

| 25                     | 34                        | 0.0435           | 0.01      | 158.02                     | 0.046            | 0.01         | 140                        | 0.042            | 0.01      |

| 50                     | 47.5                      | 0.072            | 0.01      | 343.9                      | 0.12             | 0.01         | 317                        | 0.118            | 0.01      |

|                        |                           |                  |           |                            |                  |              |                            |                  |           |

#### TABLE IV RESULTS OF FILTER CAPACITOR (Co) VARIATION.

Fig.17 Effect on output voltage  $(V_0)$  due to variation in filter capacitor  $(C_0)$

When the value of filter capacitor ( $C_0$ ) increases up to two thousand times of the designed value then output voltage ( $V_0$ ) overshoot and settling time continuously increases however rise time decreases and finally attain a constant value. If the values of filter capacitor ( $C_0$ ) decreases up to hundred times from the designed value then output voltage ( $V_0$ ) overshoot decreases, settling time and rise time remains constant.

(An ISO 3297: 2007 Certified Organization)

## Vol. 3, Issue 2, February 2014

Fig.18 Effect on inductor current (IL<sub>i</sub>) due to variation in filter capacitor (C<sub>0</sub>)

When the value of filter capacitor ( $C_0$ ) increases up to two thousand times of the designed value then boost inductor current ( $I_{Li}$ ) overshoot and settling time continuously increases however rise time remains constant value. If the values of filter capacitor ( $C_0$ ) decreases up to hundred times from the designed value then boost inductor current ( $I_{Li}$ ) overshoot decreases, settling time and rise time remains constant.

Fig.19 Effect on inductor current (IL<sub>0</sub>) due to variation in filter capacitor (C<sub>i</sub>)

When the value of filter capacitor ( $C_0$ ) increases up to two thousand times of the designed value then output filter inductor current ( $I_{Lo}$ ), settling time continuously increases however rise time decreases and finally attain a constant value. If the values of filter capacitor ( $C_0$ ) decreases up to hundred times from the designed value then filter inductor current ( $I_{Lo}$ ) overshoot become constant, settling time slowly decreasing and rise time increased.

#### IV. CONCLUSION

The parametric variation analysis of non-isolated CUK converters has been carried out for constant voltage applications considering inductor and capacitor as performance parameters. Non-isolated CUK converter has been designed to deliver 400 volts DC to a 400 watt load. Performance and applicability of this converter is presented on the basis of simulation in MATLAB SIMULINK. The design concepts are validated through simulation and results obtained show that a closed loop system using buck-boost converter will be highly stable with high efficiency. Cuk converter can be used for universal input voltage and wide output power range. The Cuk converter uses capacitive energy transfer. In the Cuk converter overshoot and settling time varies much if there is small change in boost capacitor. The closed loop Cuk converter has an efficiency of 98.69%.

#### REFERENCES

<sup>[1]</sup> Sanjeev Singh and Bhim Singh, "A Voltage-Controlled PFC Cuk Converter-Based PMBLDCM Drive for Air-Conditioners," in Proc. IEEE TRANS. ON INDUSTRY APPLICATIONS, VOL. 48, NO. 2, Apr. 2012, pp. 832-838.

<sup>[2]</sup> Sanjeev Singh and Bhim Singh, "Power quality improved PMBLDCM drive for adjustable speed application with reduced sensor buck-boost PFC converter" in proc. IEEE 11th ICETET, 2011, pp.180-184.

<sup>[3]</sup> Sanjeev Singh and Bhim Singh, "Comprehensive study of single-phase AC-DC power factor corrected converters with high-frequency isolation" IEEE Trans. on Industrial Informatics, vol. 7, no. 4, Nov. 2011, , pp. 540-556.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 3, Issue 2, February 2014

[4] Boopathy.K and Dr.Bhoopathy Bagan .K, "Buck Boost converter with improved transient response for low power applications" in Proc. IEEE SIEA, Sep 2011, pp. 155-160.

[5] Altamir Ronsani and Ivo Barbi, "Three-phase single stage AC-DC buck-boost converter operating in buck and boost modes" in Proc. IEEE, 2011, pp.176-182.

[6] Sanjeev Singh and Bhim Singh, "An adjustable speed PMBLDCM drive for air conditioner using PFC Zeta converter," Int. J. Power Electron. (IJPElec), vol. 3, no. 2, pp. 171–188, Apr. 2011.

[7] Sanjeev Singh and Bhim Singh, "Power Electronics, Drives and Energy Systems (PEDES)," in Proc. IEEE PEDES'2010.

[8] Sanjeev Singh and Bhim Singh, "Single-phase power factor controller topologies for permanent magnet brushless DC motor drives," in IET Power Electron., 2010, Vol. 3, Iss. 2, pp. 147–175.

[9] Sanjeev Singh and Bhim Singh, "A voltage controlled adjustable speed PMBLDCM drive using a single-stage PFC half-bridge converter," in *Proc. IEEE APEC'10*, 2010, pp. 1976–1983.

[10] Marcos Orellana, Stephane Petibon and Bruno Estibals, "Four switch buck-boost converter for photovoltaic DC-DC ower applications" in proc. IEEE, ISGE, 2010, pp.469-474.

[11] B. Singh, B. N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, and D. P. Kothari, "A review of single-phase improved power quality ac-dc converters," *IEEE Trans. Ind. Electron.*, vol. 50, no. 5, pp. 962–981, Oct. 2003.

[12] S. M. Ćuk, "Modeling, Analysis, and Design of Switching Converters," Ph.D. dissertation, California Institute of Technology, Pasadena, Nov. 1976.

#### BIOGRAPHY

**Rheesabh Dwivedi** received his B.Tech degree in Electrical & Electronics Engineering from Uttar Pradesh Technical University, Lucknow in 2010. He also obtained the M.Tech degree in Instrumentation & Control Engineering from Sant Longowal Institute of Engineering and Technology, Longowal Dist-Sangrur (Punjab) in 2013. He served as assistant professor in Gokaran Narvadeshver Institute of Technology & Management, Lucknow (U.P). His area of interest includes Power Electronics, Control System and Electrical Drives. He is currently an Assistant Professor at the Department of Electrical Engineering in Teerthanker Mahaveer University, Moradabad (U.P), India

**Vinay Kumar Dwivedi** received his M.Tech degree in Power Electronics & ASIC design from Motilal Nehru National Institute of Technology (MNNIT), Allahabad, U.P. in 2013 and graduated from Uttar Pradesh Technical University, Lucknow, U.P., India in 2008. He was a Faculty member with Dr. K. N. Modi Institute of Engineering & Technology, Ghaziabad, U.P. for about two years and then was with the MIT, Ghaziabad for about one year. His areas of interest are Power electronics, Power Quality, Network and Control System. He is currently an Assistant Professor at the Department of Electrical Engineering in Teerthanker Mahaveer University, Moradabad (U.P), India.

**Rahul Sharma** completed his B.Tech degree in Electrical Engineering from Uttar Pradesh Technical University,Lucknow in 2011. His area of interest includes Power Electronics, Control System and Electrical Machines. He is currently a Lecturer at the Department of Electrical Engineering in Teerthanker Mahaveer University, Moradabad (U.P), India.