# Performance Analysis and Designing 16 Bit Sram Memory Chip Using XILINX Tool

#### Monika Solanki\*

Department of Electronics & Communication Engineering, MBM Engineering College, Jodhpur, Rajasthan

# **Review Article**

Received date: 07/12/2016

Accepted date: 18/01/2017

Published date: 24/01/2017

#### \*For Correspondence

Monika Solanki, Department of Electronics & Communication Engineering, MBM Engineering College, Jodhpur, Rajasthan, India, Tel: 0291-2551566.

E-mail: rahulliger19@gmail.com

Keywords: Electronic design automation (EDA),

SRAM

#### **ABSTRACT**

e-ISSN:2319-9873

In this paper a memory chip has been designed with the size of 16 bit using Xilinx software. For all those memory applications which requires high speed for example - in cache, SRAM is most often used. Xilinx ISE is an Electronic Design Automation (EDA) tool that allows integration in a single framework, different applications and tools (both proprietary and from other vendors), allowing to support all the stages of IC design and verification from a single environment. This tool is completely general, and supports different fabrication technologies. When we select a particular technology, a set of configuration and technology-related files are employed for customizing the Xilinx environment.

# INTRODUCTION

Fast low power SRAMs are becoming the critical component of many VLSI chips. There is increasing divergence in the speed of the processors and the main memory, and the power dissipation is also increasing due to increase in the integration and the operating speed as well as increase in the battery powered devices. The SRAM helps in bridging the gap and also reducing the power dissipation [1]. After designing the memory, we will go for testing the fault in the memory.

#### Why Use a SRAM?

There are many reasons due to which we use an SRAM in a system design. Design tradeoffs will include density, speed, volatility, cost, and many other features. All these factors should be considered before selecting a RAM for designing our system. Let us discuss all these factors in brief:

**Speed:** The primary and the foremost advantage of an SRAM over DRAM is its speed. The fastest DRAMs on the market still requires five to ten processor clock cycles to access the first bit of data.

**Density:** DRAMs have significantly higher densities than the largest SRAMs because of the way DRAM and SRAM memory cells are designed.

**Volatility:** The SRAM memory cells require more space on the silicon chip, but they have other advantages that translate directly into improved performance. Unlike DRAMs, SRAM cells do not need to be refreshed. They are available for reading and writing data 100% of the time.

**Cost:** If cost is the major factor in a memory design, then DRAMs will be the best to use instead of SRAM. If, on the other hand, performance is a critical factor then using a well-designed SRAM is an effective and cost performance solution for us.

**Custom features:** Most DRAMs come in only one or two flavors or forms. Due to which the cost of them remains down, but this does not help when you need a particular kind of addressing sequence, or some other custom feature.

## **BASIC ARCHITECTURE**

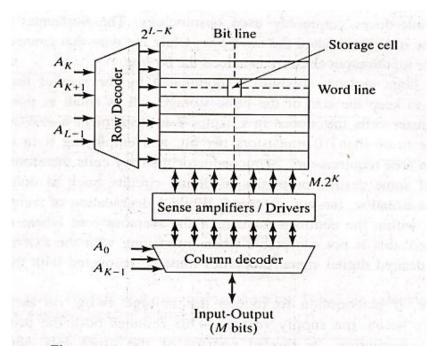

The general block diagram of a typical SRAM is shown in **Figure 1** below. SRAM can be organized in two ways. It can be organized either as bit oriented or as word oriented [2]. In the first case that is bit oriented SRAM, each address accesses a single bit, whereas in the other case that is word oriented memory, each address will access a word. The length of the word will be of n bits.

# Research & Reviews: Journal of Engineering and Technology

The main SRAM building blocks include various components. All these components or blocks used in the SRAM are listed as follows:

- SRAM Cell

- Pre-Charge Circuit

- Write Driver circuit

- Sense Amplifier

- Row Decoder

Figure 1. SRAM array architecture.

## **Sram Cell**

A Typical SRAM cell is made up of six MOSFETs. The number of these MOSFETs can vary. Each bit in an SRAM is stored on four transistors named as (M1, M2, M3, and M4). These transistors form two cross – coupled inverters [3]. This storage cell has two stable states which are denoted by 0 and 1. Other two additional access transistors are used to control the access to a storage cell during read and write operations. In addition to such six – transistor (6T) SRAM, other kinds of SRAM chips use 4, 8, 10 also called (4T, 8T, 10T SRAM), or more transistors per bit.

Sram cell operation: An SRAM cell has three different states. These states are described in brief as below. It can be in:

- · Standby (where the circuit is idle)

- Reading (in which the data has been requested)

- Writing (helps in updating the contents)

#### **Precharge Circuit**

The pre-charge circuit is one of the vital components that are constantly used within SRAM cell. The aim of the pre-charge is to charge the bit and bit line bar to Vdd=1.8v. As the name suggests, pre-charge is used for charging something or some devices [4]. The pre-charge circuit sets the bit lines to be charged high at all times throughout the read and write operation.

#### **Driver Circuit**

The driver circuit is one of the basic and important components in the memory design circuit. Its job is to bring the bit line and bit line bar to ground potential for the further job or operation. Before this the bit line and bit line are being charged maximum supply voltage Vdd through the pre-charge circuit.

With pre-charge circuit it was get charged and after that it gets discharged with the help of the driver circuit. It is also known as write driver. The driver gets enabled by the word enable which is connected in the upper part of the circuit.

The bit line which is close to the O logic will get discharged first, after that its logic gets inverted or complimented. In the

e-ISSN:2319-9873

# Research & Reviews: Journal of Engineering and Technology

similar manner the bit line and bit line bar gets discharged to the ground [5]. With this kind of operation the bit line and bit line bar gets discharged.

#### **Sense Amplifier**

Sense amplifiers are the vital component in the memory designing process. The job of the sense amplifier is to sense the bit line and bit line bar for proper monitoring action. It improves the speed of the read and writes operation of the memory cell. It's another job or work is to reduce the power needed for the operation or we can say decrease the power consumption <sup>[6]</sup>. The sense amplifiers major task is the amplification of the voltage difference which is being produced on the bit line and bit line bar at the time of operation.

Sense amplifiers play a major role in the functionality, performance and reliability of memory circuits.

Functions of sense amplifier: Following are the functions of the sense amplifier which are listed below:

- Amplification

- Delay Reduction

- Power Reduction

#### Decoder

Decoder is a combinational circuit that is used to convert the binary information from n input lines to a maximum of 2n unique outputs lines. Enable inputs must be on or it must be high for the decoder function; otherwise its outputs assume a single "disabled" output code word. By doing this the binary input conversion gets easier with the operation and we can get the desired output from this kind of combinational output [7,8]. We can use these output lines for the number of operations like data, word line selection for the memory cell and also for the other digital information storage purpose.

## SIMULATION RESULTS

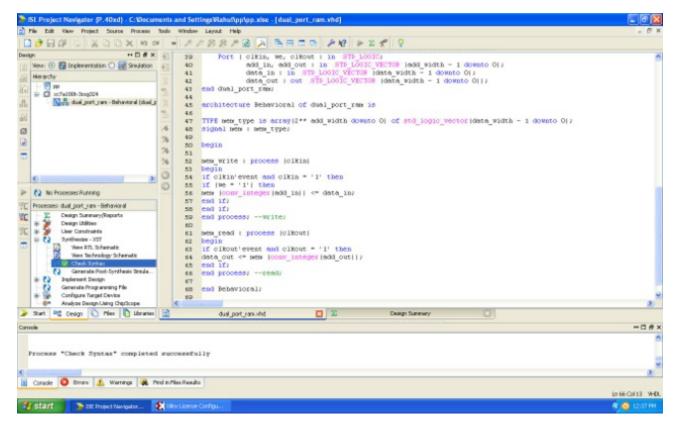

Reduction of power dissipation or power consumption in the memories is becoming of premier importance in the arena of digital design [9-11]. Portable applications are lowering the bar on how much power memory may be consumed. The program written in the Xilinx ISE Webpack is shown in **(Figure 2)**.

Figure 2. Program written in xilinx software.

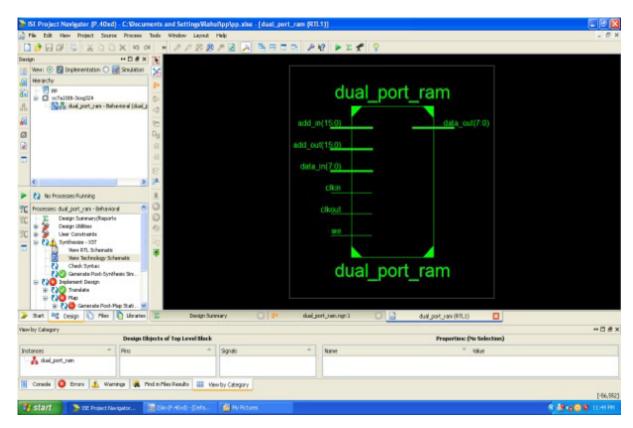

The program is written and the syntax is checked successfully. After this we have created RTL schematic. For this the software first asks for the selection of the elements [12:14]. After selecting the elements we have to click on the tab Create Schematic. As soon as we click on this tab, we see the RTL schematic of the program (Figure 3).

e-ISSN:2319-9873

Figure 3. RTL schematic in xilinx software.

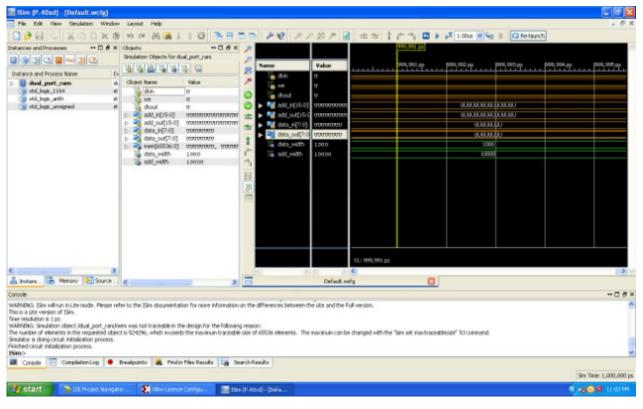

After doing all this we will simulate the VHDL code using the ISim simulator. The waveforms of all the input and output parameters are displayed on the screen [10,11]. We can then provide the input and observe the output (**Figure 4**).

Figure 4. Waveform in xilinx software.

# CONCLUSION

The simulated waveforms have shown that the architecture is an effective testing method to design embedded memories as it offers various advantages. In this project we have discussed about the simulation result that is being done for the above

# Research & Reviews: Journal of Engineering and Technology

memory cell. The work is being carried out with Xilinx design software with read and writes operation in the above layout. We have designed a 16 bit memory cell with this software. The stop time of the cell is 10ns. The duration of write enable and sense enable set to 5ns. The pre-charge level is Vdd/2. The delay in the decoder circuit is 270 ps. For which we are getting the output that follows to the inputs but after some interval of time due to delay.

## **REFERENCES**

- 1. Fischerova M and Simlastik M. MemBIST Applet for Learning Principles of Memory Testing and Generating Memory BIST. Digital System Design, Proceedings. 8th Euromicro Conference; 2005.

- 2. Chuanpei X, et al. BIST Method of SRAM for Network-On-Chip. Electronic Measurement & Instruments (ICEMI), 12th IEEE International Conference; 2015.

- 3. Haron NZ, et al. Modeling and Simulation of Microcode Memory Built-in Self-Test Architecture for Embedded Memories. Communications and Information Technologies. International Symposium; 2007.

- 4. Chih-Sheng H, et al. A BIST Scheme with the Ability of Diagnostic Data Compression for RAMS. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2014;33:2020-2024.

- 5. Goor JVD, et al. Generic, Orthogonal and Low-cost March Element based Memory BIST. Test Conference (ITC) 2011, IEEE International; 2012.

- 6. Bosio A, et al. An Effective BIST Architecture for Power-Gating Mechanisms in Low-Power SRAMs. Quality Electronic Design (ISQED), 17th International Symposium; 2016.

- 7. Gadde P and Niamat M. FPGA Memory Testing Technique using BIST. Circuits and Systems (MWSCAS), IEEE 56th International Midwest Symposium; 2013.

- 8. Husin MH, et al. Built in Self-Test for RAM Using VHDL. IEEE Colloquium on Humanities, Science & Engineering Research; 2012.

- 9. Manikandan P, et al. A Programmable BIST with Macro and Micro codes for Embedded SRAMs. Design & Test Symposium (EWDTS), 9th East-West; 2011.

- 10. MohdNoor N, et al. New Microcode's Generation Technique for Programmable Memory Built-In Self-Test. Test Symposium (ATS), 19th IEEE Asian; 2010.

- 11. Mrozek I and Yarmolik SV. Analyses of Two Run March Tests with Address Decimation for BIST Procedure. East-West Design & Test Symposium; 2013.

- 12. MohdNoor N, et al. Area-Effective Programmable FSM-Based MBIST for Synchronous SRAM. Quality Electronic Design, ASQED 1st Asia Symposium; 2009.

- 13. Puczko M. Low power Test Pattern Generator for BIST. Selected Problems of Electrical Engineering and Electronics (WZEE); 2015.

- 14. Shirur YJM, et al. Performance Analysis of Low Power Microcode based Asynchronous P-MBIST. Advances in Computing, Communications and Informatics (ICACCI), International Conference; 2015.

e-ISSN:2319-9873