## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, January 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

# An Optimized Successive Interference Cancellation for CI-Based Multiuser Detection Using VLSI Implementation Strategy

Geo.H.Provin<sup>1</sup>, K.Sowmya<sup>2</sup>

PG Student, Department of ECE, DMI College of Engineering, Chennai-600123, India<sup>1</sup> Assistant Professor, Department of ECE, DMI College of Engineering, Chennai-600123, India<sup>2</sup>

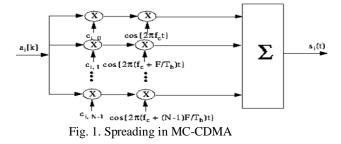

Abstract: In this project, we proposed variable rate carrier interferometry multicarrier code division multiple access (CI/MC-CDMA) multiuser transceiver that achieves a data rate of minimum 1Gbps equivalent to the 4G standard of IEEE. Multiple **Carrier -Code Division Multiple Access (MC-CDMA)** is the combination of Code Division Multiple Access (CDMA) and Orthogonal Frequency Division Multiplexing (OFDM), therefore the advantages of both schemes can be achieved. In MC-CDMA scheme each data symbol is spreaded in frequency domain and transmitted on different subcarrier which eliminates frequency selective fading and show significant improvement in bit error rate performance. The proposed non-contiguous allocation improves the Performance of variable rate system over frequency selective Channel. In receiver side through iterative successive interference cancellation complexity is reduced considerably. The proposed successive interference cancellation strategies for a detector, is suitable for implementation in VLSI. Simulations are carried out for all the possible data rate schemes, results show that for the given users and BER of proposed algorithm comparatively gives far better results.

## Keywords- CI, MC-CDMA, OFDM, BER, VLSI,Successive interference cancellation.

#### I. INTRODUCTION

Code Division Multiple Access (CDMA) technology is a continuing driving force behind wireless networks around the globe and according to the CDMA Development Group (CDG), there were 431 million CDMA subscribers and 91million CDMA 2000 1x subscribers worldwide by the end of the year 2007. It is believed that there will be many operators who will regard the HSPA+ and EV-DO

#### Copyright to IJIRSET

Rev B path as an easier and safer way into higher data rates. Furthermore, an upgrade to HSPA+ is generally considered cheaper than a move to LTE since LTE is based on MCCDMA and a number of new components will be required. It is therefore expected that by the year 2017, mobile MCCDMA solutions such as LTE, UMB and mobile Wi-MAX will only account for 6.4% of the global number of cellular subscriber. Multi-Carrier Code Division Multiple Access (MC-CDMA) is a multiple scheme used in MCCDMA-based access telecommunication systems, allowing the system to support multiple users at the same time. MC-CDMA and multiplexed MC-CDMA on the basis of which domain DS spreading takes place, there are also, two alternative schemes which are (1) time-spreading MC-CDMA, and (2) frequency-spreading MC-CDMA. Therefore, by mixing all of them in various combinations, we will have four different MC-CDMA systems.

#### II. DESIGN ANALYSIS OF MC-CDMA TRANSMITTER SIDE

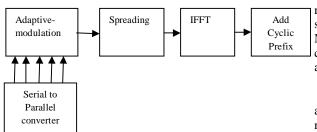

The transmitter side consists of serial to parallel converter, after that there is adaptive modulation through which different modulations can be adapted(BPSK,QPSK,QAM). Then the pn-sequence are generated through LFSR(Linear Feedback Shiftregister) and gets spreaded through spreading and passed through

## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, January 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

the IFFT block, then to avoid inter-symbol interference cyclic prefix is added.

Fig 2.MC-CDMA Transmitter side block diagram

### III. DESIGN ANALYSIS OF MC-CDMA RECEIVER SIDE

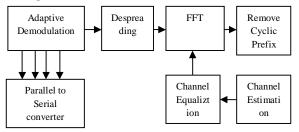

In the receiver side channel estimation block is used to find the errors or interference generated in that particular modulation .So after that channel equalization block is used which is used to equalize the error upto its limit. After this the reverse process of transmitter side takes place.

#### Fig 3.MC-CDMA Receiver side block diagram

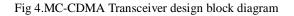

#### IV. DESIGN ANALYSIS OF MC-CDMA TRANSCEIVER

The need for supporting ever increasing data rates while maintaining high quality of service is the result of the penetration of digital technology into formerly analog services (e.g. radio an Television broadcasting), of the demand for mobility in case of typically fixed services (e.g. LAN and Internet access), of the long outstanding promise for certain wideband services to the home (e.g. video on demand and video conferencing) and of the evolution of currently existing cellular communication system. The generally accepted system architecture of these new systems involves a wired backbone with wireless access to the users' terminals which, depending on the application, can be hand-held, portable or fixed. It is this "last mile" that has been attracting focus lately.To illustrate, there is an ongoing research effort for defining and/or developing such systems as LMCS/LMDS, Hyper LAN, wireless LAN, the NII/GII1, third and fourth generation mobile communications, ad-hoc personal area communications, and communications in the unlicensed frequency bands.

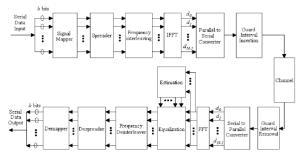

The MC-CDMA system includes a transmitter and a receiver. The block diagram of a transmitter and receiver is shown below.

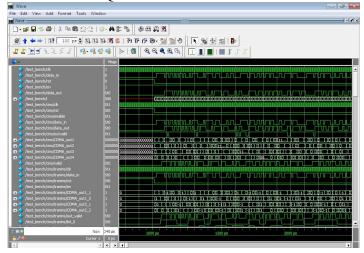

#### V. OUTPUTWAVEFORMS AND POWER AREA FREQUENCY ANALYSIS

Fig 5.Simulated output

## Copyright to IJIRSET

## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, January 2014

International Conference on Engineering Technology and Science-(ICETS'14)

## On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

#### AREA UTILIZATION REPORT:

| nmary                              |                                         |

|------------------------------------|-----------------------------------------|

|                                    |                                         |

| Flow Status                        | Successful - Sat Oct 19 04:36:14 2013   |

| Quartus II Version                 | 9.0 Build 132 02/25/2009 SJ Web Edition |

| Revision Name                      | CDMA                                    |

| Top-level Entity Name              | Transmitter_module                      |

| Family                             | Cyclone III                             |

| Met timing requirements            | N/A                                     |

| Total logic elements               | 26 / 5,136 ( < 1 % )                    |

| Total combinational functions      | 22 / 5,136 ( < 1 % )                    |

| Dedicated logic registers          | 23 / 5,136 ( < 1 % )                    |

| Total registers                    | 23                                      |

| Total pins                         | 69 / 183 ( 38 % )                       |

| Total virtual pins                 | 0                                       |

| Total memory bits                  | 0 / 423,936 ( 0 % )                     |

| Embedded Multiplier 9-bit elements | 0 / 46 (0%)                             |

| Total PLLs                         | 0/2(0%)                                 |

| Device                             | EP3C5F256C6                             |

| Timing Models                      | Final                                   |

#### FREQUENCY PERFORMANCE REPORT:

| n | max Summai    | ry                     |                   |                                                                                                                                                                                                                                                                                                                   | 9 |

|---|---------------|------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1 | Fmax          | Restricted Fmax        | Clock Name        | Note                                                                                                                                                                                                                                                                                                              |   |

| l | 612.75 MHz    | 250.0 MHz              | clk               | limit due to minimum period restriction (max I/O toggle rate)                                                                                                                                                                                                                                                     |   |

| 1 |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

| I |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

| J |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

| 1 | ource and dea | stination registers of | or ports are driv | lesign, regardless of the user-specified clock periods. FMAX is only computed for paths where the<br>en by the same clock. Paths of different clocks, including generated clocks, are ignored. For paths<br>puede as if the rism and falline deces are scaled along with FMAX, such that the duty cycle (in terms |   |

|   |               |                        |                   | ds that you always use clock constraints and other slack reports for sign-off analysis.                                                                                                                                                                                                                           |   |

|   |               |                        |                   |                                                                                                                                                                                                                                                                                                                   |   |

#### VI. CONCLUSION AND FUTURE WORK

Hence through our project the area utilization, frequency for fast and slow corners, and static and dynamic power dissipations are calculated using quatrus-11 software. The quatrus-11 softer is electronic device automation because for our coding it will generate hardware circuits design. Therefore in mc-cdma the interference is reduced while the throughput is increased and is shown as a modelsim output. As a result Copyright to JJIRSET w combination of gsm and cdma results in an less interference and high throughput environment. For the future enchancement it can be Implemented in real time as well as the throughput can be improved beyond 1gbps.

#### REFERENCES

- Cottatellucci L, Muller R. R. and Oebbah M, 2010, Asynchronous COMA System with Random Spreading - Part I : Fundamental Limits, IEEE Transactions on Information Theory, Volume : 56, Issue : 4, Pages 1477-1497

- 00 G. L and Feher K., 1996, Efficient Filter Oesign for IS-95 COMA Systems, IEEE Transactions on Consumer Electronics, Volume: 42, Issue: 4 Pages 10 11 - 1020.

- Boukadourn M., Tabari K., Bensaoula A, Starikov o. and Aboulhanid E. M., 2005, FPGA Implementation of a COMA Source Coding and Modulation Subsystem for a Multiband Fluorometer with Pattern Recognition C apabilities, IEEE International Symposium on Circuits and Systems, Volume : 5, Pages 4767 - 4770.

- Clarke P. and de Lamare R. C, 2011, Low-Complexity Reduced-Rank Linear Interference Suppression Based on Set-Membership Joint Iterative Optimization for OS-COMA Systems, IEEE Transactions on Vehicular Technology, Volume : 60, Issue : 9, Pages 4324 - 4337.

- Vishwas Sundaramurthy and Joseph C avallaro, 1999, A Software Simulation Testbed for Third Generation COMA Wireless Systems, Proc. 33,d Asilomar Conf on Signals, Systems and Computers, Pacific Grove C A

- Uuanbin Guo, Dennis McCain and Joseph R C avallaro, 2004, Low Complexity System-on-Chip Architecture of Parallel- ResidueCompensation in CDMA Systems, ISCAS, Pages : IV 77 – 80

- Neiyer S Correal, Michael Buehrer R and Brian D. Woerner, 1999, A DSP-Based DS-CDMA Multiuser Receiver Employing Partial Parallel Inference Cancellation, IEEE Journal on Selected Areas in Communications Volume: 17 No. 4, Pages 613-630.

- Tomaso Erseghe and Antonio Maria Cipriano, 2011, Maximum Likelihood Frequency Offset Estimation in Multiple Access TimeHopping UWB, IEEE Transactions on Wireless Communications, Volume: 10, No. 7, Pages 2040 -2045.

- Theodore S Rappaport, 2010, "Wireless Communication Principles and Practices", 2ND Edition, Pearson Education, Dorling Kindersley (India) Pvt Ltd.

- Min Shi D'Amours, C. Yongacoglu, A. 2010, Design of spreading permutations for MIMO-CDMA based on spacetime block codes, Communications Letters, IEEE, Volume: 14 Issue: 1, Pages: 36 - 38.

- Magaa, ME, Rajatasereekul, T., Hank, D. and Hsiao-Hwa Chen, 2007, Design of an MC-CDMA System That Uses Complete Complementary Orthogonal Spreading Codes", IEEE Transactions on Vehicular Technology, Volume: 56, Issue: 5, Pages: 2976 - 2989.

- 12. [12] Alaka Barik and Asutosh Kar, 2011, ICI Self-Cancellation Method of BPSK OFDM, IJCA Proceedings on International Conference on VLS1, Communications and Instrumentation (ICVCI) (15), Published by Foundation of Computer Science, Pages 12-14.

www.ijirset.com