(An ISO 3297: 2007 Certified Organization) Vol.2, Special Issue 1, March 2014 Proceedings of International Conference On Global Innovations In Computing Technology (ICGICT'14)

## **Organized** by

Department of CSE, JayShriram Group of Institutions, Tirupur, Tamilnadu, India on 6<sup>th</sup> & 7<sup>th</sup> March 2014

# Power Optimization in FPGA through Controller Device

## V.Pavithra, T.Suganya, V.Suganya

ABSTRACT: Field programmable Gate Arrays (FPGAs) are widely used for implementation of digital system design due to their flexibility, low time-to-market, growing density and speed. But the power consumption, especially leakage and dynamic power has become a major concern for semiconductor industries. FPGAs are less power efficient than custom ASICs, due to the overhead required providing programmability. Despite this, power has been largely ignored by the FPGA research community earlier, whose prime focuses on power too. Hence this paper demonstrates some of the most utilized and efficient techniques for power optimization and reduction in FPGAs currently. The Clock gating methodology based on voltage scaling is proposed in this paper. Dual Supply voltage design is widely accepted as an effective way to reduce the power consumption of CMOS circuit. The Coarse Grained Clock network technique is utilized to minimize clock network power in FPGA device.

KEYWORDS FPGA, Power Reduction, clock skew, dual Vdd.

#### I. **INTRODUCTION**

Field-Programmable Gate Arrays (FPGAs) are integrated circuits that can be programmed to implement any digital circuit. The main difference between FPGAs and conventional fixed logic implementations, such as Application Specific Integrated Circuits (ASICs), is that the designer/customer programs the FPGA on-site[1-3].For fixed logic, the designer must create a layout mask and send it to a foundry to be fabricated. Creating a layout is labor-intensive and requires expensive CAD tools and experienced engineers. Programmable switches controlled by configuration memory occupy a large area in the FPGA and add a significant amount of parasitic capacitance and resistance to the logic and routing resources.

Many studies have focused on reducing the speed and area overhead of FPGAs. Important advancements include clusterbased logic blocks[4], which improve speed by grouping the basic logic elements of the FPGA into clusters with faster local interconnect; embedded memories[5], which reduce the speed and area overhead for applications with storage requirements; and embedded ALUs[6], which reduce at the speed and area overhead for applications that perform arithmetic operations. As CMOS process technology scales down, the power density continues to increase due to higher chip operating frequencies, higher total interconnect capacitance per chip, and increasing leakage. Indeed, the International Technology Roadmap for semiconductors has identified low-power design techniques as a critical technology need[7].

## POWER CONSUMPTION

Due to the dramatic increase in portable and battery-operated applications, lower power consumption has become a necessity in order to prolong battery life. Power consumption is an important part of the equation determining the end product's size, weight, and efficiency. FPGAs are becoming more attractive for these applications due to their shorter product life cycle. FPGAs are programmable, so they allow product differentiation. Selecting an appropriate FPGA architecture is critical in achieving the best static and dynamic power consumption. As per we are dealing with Power optimization & reduction techniques. The two components to power consumption: static, dynamic. Copyright @ IJIRCCE www.ijircce.com

(An ISO 3297: 2007 Certified Organization)

Vol.2, Special Issue 1, March 2014

## **Proceedings of International Conference On Global Innovations In Computing Technology (ICGICT'14)**

## Organized by

## Department of CSE, JayShriram Group of Institutions, Tirupur, Tamilnadu, India on 6th & 7th March 2014

Dynamic power is the power dissipated during active state due to switching activity of input signal [5]. In other words, dynamic power dissipation is caused by the charging. Since an input can change without necessarily resulting in logic transition in the output, dynamic power can be dissipated even when an output does not change its logic state. The dynamic power dissipation is the result of charging and discharging parasitic capacitances. Dynamic power dissipation in a circuit is given as,

$$P_{dynamic} = \sum (\alpha f_{clk} C_L V_{dd}^2)$$

Where C is the load capacitance,  $V_{dd}$  is the operating voltage, $\alpha$  is the activity factor of that net (the probability that net will switch in a given cycle) and f is the operating frequency of the node. The techniques to reduce Dynamic Power consumption are, Clock Gating, Power Gating, Improved switching activity, Glitch removal, Pipelining, Guarded Evaluation.

## II. LITERATURE SURVEY:

In previous work single voltage is applied to the whole circuit. The power consumed is high as both active and inactive blocks use the same supply voltage. This power consumption degrades the system performance and life time of portable application. In order to overcome this drawback, we propose dual Vdd technique along with controller device. As the switching power is quadratically related to the supply voltage, the power consumption is effectively reduced.

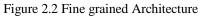

Power gating techniques can be classified into two types: coarse-grain power gating and fine-grain power gating. Low power FPGA architecture is generated with the use of fine grained Vdd control scheme called micro Vdd-hoping[8]. The Vdd of each block is varied between the higher  $V_{DD}$  and lower  $V_{DD}$  spatially and temporalily to achieve low power. In fine grained power gating technique each lookup table have its own controller device. So the number of controllers used in fine grained technique is much larger than that of coarse grained technique. In this technique the controller device is always running. This results in large area and dynamic power overheads. Due to these overheads fine grained technique is less efficient than the coarse grained technique.[9]

(An ISO 3297: 2007 Certified Organization) Vol.2, Special Issue 1, March 2014

Proceedings of International Conference On Global Innovations In Computing Technology (ICGICT'14)

## Organized by

Department of CSE, JayShriram Group of Institutions, Tirupur, Tamilnadu, India on 6<sup>th</sup> & 7<sup>th</sup> March 2014

Figure 2.1 Coarse grained Architecture

(An ISO 3297: 2007 Certified Organization)

Vol.2, Special Issue 1, March 2014

Proceedings of International Conference On Global Innovations In Computing Technology (ICGICT'14)

## Organized by

## Department of CSE, JayShriram Group of Institutions, Tirupur, Tamilnadu, India on 6th & 7th March 2014

In coarse-grain power gating, a large number of LUTs share a single sleep controller so the area and power overheads of the sleep controller are relatively small.

## **III. PROPOSED METHOD**:

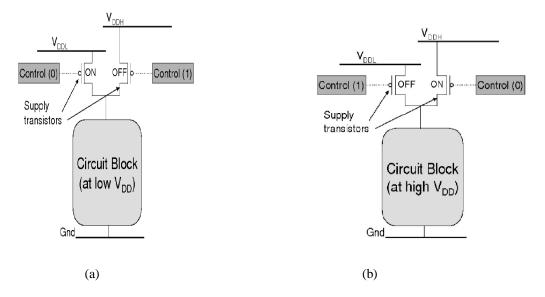

Reducing the supply voltage ( $V_{DD}$ ) is an effective technique for reducing both dynamic and static power. Dynamic power has a quadratic dependency on supply voltage, while both sub-threshold leakage and gate leakage exhibit exponential dependencies on the supply voltage. However, reducing supply voltage also negatively affects circuit performance. A well-known technique to reap the benefits of voltage scaling without the performance penalty is the use of dual- $V_{DD}$ . The active blocks in the design operate on the normal  $V_{DD}$  (or  $V_{DDH}$ ), while inactive blocks operate on a second supply rail with a lower voltage (or  $V_{DDL}$ ). While dual-  $V_{DD}$  ICs have been successfully used in low-power ASICs and custom ICs [12], no commercial FPGA today uses multiple  $V_{DD}$  for power reduction. The difficulty of designing a dual- $V_{DD}$  FPGA is that the optimal  $V_{DD}$  assignment changes from one design to another.

Consequently, if logic blocks are statically determined to be operating at low or high  $V_{DD}$ , the placement and routing algorithms need to be modified accordingly as in [11]. However, static assignment of  $V_{DD}$  to the blocks may prevent the ability to reduce power consumption or to meet timing constraints for some designs. In contrast, the use of  $V_{DD}$  programmability for each block helps to tune the number of high and low  $V_{DD}$  blocks as desired by the application. In this approach, the challenge is in determining the  $V_{DD}$  assignments to each block. Furthermore, positioning of the controller influences the ability to assign lower  $V_{DD}$  to the routing blocks. In our programmable dual- $V_{DD}$  architecture (figure 3.1), the  $V_{DD}$  of a circuit block is selected between  $V_{DDH}$  and  $V_{DDL}$  by using two high-VT transistors (supply transistors) connecting the block to the supplies. The state (ON/OFF) of each supply transistor is controlled by a configuration bit.

Figure 3.1 Supply Transistors used for programmable  $V_{DD}$

International Journal of Innovative Research in Computer and Communication Engineering(An ISO 3297: 2007 Certified Organization)Vol.2, Special Issue 1, March 2014Proceedings of International Conference On Global Innovations In Computing Technology (ICGICT'14)

## Organized by

Department of CSE, JayShriram Group of Institutions, Tirupur, Tamilnadu, India on 6th & 7th March 2014

## IV. SIMULATION RESULTS

Comparison is made for various supply voltage scaling and it is found that power consumed by our Dual  $V_{DD}$  technique is lesser than without controller device and also  $I_{dd}$  is analyzed in Table4.1.

| WITHOUT CONTROLLER |           |                      | WITH CONTROLLER                                    |           |                      |

|--------------------|-----------|----------------------|----------------------------------------------------|-----------|----------------------|

| Voltage(V)         | Power(mW) | I <sub>dd</sub> (mA) | Voltage(V)<br>V <sub>DDH</sub><br>V <sub>DDL</sub> | Power(µW) | I <sub>dd</sub> (mA) |

| 1                  | 0.107     | 1.186                | 1 0.8                                              | 48.153    | 1.205                |

| 3.3                | 0.143     | 1.169                | 3.3<br>1.2                                         | 85.326    | 1.186                |

Table 4.1Comparison of Power Dissipation without Controller and with Controller

## V. CONCLUSION

We have presented a dual- $V_{DD}$  FPGA architecture that provides significant power savings with minimal performance penalty. Variations of the  $V_{DD}$  assignment and controller device were explored. The dynamic power was reduced around 45- 60%. Power supply network to support dual  $V_{DD}$  or configurable  $V_{DD}$  may introduce extra routing congestion. The total power reduction percentage for dual  $V_{DD}$  FPGAs is significantly lower than the logic power reduction percentage. we will study how to reduce interconnect power by dual  $V_{DD}$  in future

#### REFERENCES

- [1] Xilinx, "Lowering power at 28 nm with Xilinx 7 Series FPGAs", White paper WP389(v1.1.1),2012.

- [2] Actel, "Dynamic power reduction in Flash FPGAs", White paper, 2011.

- [3] Xilinx (2011), "Power methodology guide," White paper, UG786 (v13.1).

- [4] V. Betz., J. Rose, and A. Marquardt, "Architecture and CAD for deep-submicron FPGAs", Kulwer academic publishers,1999.

- [5] S.J.E.Wilton, J. Rose, and Z.G. Vranesic, "Architecture of centralized field-configurable Programmable Gate Arrays(FPGA)", pp.97-103,1995.

- [6] S.Hong and S.S. Chin, "Reconfigurable embedded MAC core design for low-power coarse Grain FPGA", IET Electronics Letters, Volume 39, Issue 7, pp. 606-608, 2003

- [7] International Technology Roadmap for Semiconductors, 2011.

- [8] Pooran singh, santosh kumar vishvakarma,"Device/circuit/Architectural Techniques for ultra low power FPGA design", Microelectronics and solid state electronics, 2013.

- [9] Safeen Huda, Muntasir Mallick, Jason H. Anderson, "clock Gating Architecture for FPGA Power reduction".

- [10] A.Gayasen, K.Lee, N.Vijay Krishnan, M.Kandemi, M.J.Irwin, T.Tuan, "A Dual VDD Low power FPGA Architecture", Pennsylvania state University.

- [11] F.Li, D.Chen, L.He, and J.Cong."Low-power FPGA using pre-Defined Dual-V<sub>DD</sub>/Dual-Vt Fabrics". In Proceedings of ACM/SIGDA International Symposium on Field Programmable gate arrays, 2004.

- [12] M.Takahashi et.al."A 60-mW MPEG4 Video Codec using Clustered Voltage Scaling With Variable Supply-voltage Scheme", in IEEE Journal of solid state circuits, vol.33, No.11, Nov1998