(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 11, November 2013

# **REDUCTION OF PAPR USING PTS AND SLM OF OFDM TRNSCIEVER SYSTEM**

Neenu Joseph<sup>1</sup>, Dr. P Nirmal Kumar<sup>2</sup>

Research Scolar, Dept. of ECE, College of Engineering Guindy, Anna University, Chennai, Tamilnadu, India<sup>1</sup>

Associate Professor, Dept. of ECE, College of Engineering Guindy, Anna University, Chennai, Tamilnadu, India<sup>2</sup>

**ABSTRACT**: This paper proposes the physical layer design and architecture of Software Defined Radio (SDR). In this SDR the OFDM (Orthogonal frequency Division multiplexing) technique BPSK or 16 QAM is used as modulation. The modulations can be selected according to the signal to noise ratio. The peak to power average ratio can be reduced by dividing the input bits as Partial Transmit Sequence (PTS). The divided bits can be selected by using selective mapping (SLM). The size of FFT is scalable and can be select according to the size transmission bits. The reconfigurability of FPGA allows the receiver to select the modulation at run time without changing the current program. The run time reconfiguration reduces the complexity in modification..

Keywords: SDR, Run time Reconfiguration, OFDM, BPSK, QPSK, PAPR reduction algorithms

## **I.INTRODUCTION**

According to the advances in the technologies in wireless communication, the customer needs also increased to communicate in any place with different accessories. The advances in the wireless communication lead to evolution of very efficient radio receivers. Software defined Radio affords an attractive nature of reconfigurable and multimode operations.

SDR is a collection of Hardware and software in which all the radio functions can be implemented using software coding or firmware on a processing system. These software can be alterable according to the applications in communication system. The processing systems include Field Programmable Gate Arrays (FPGA), Digital Signal Processors (DSP), General Purpose Processors (GPP), Programmable System on Chip (SoC) or other Application Specific Programmable Processors [1]. The use of SDR technologies allows new wireless features like Third Generation (3G) and Fourth Generation (4G) capabilities to be added to existing Generation for mobile applications and radio systems without requiring new hardware.

Software defined radio (SDR) – an idea of moving hardware components into software – helps reducing the complexity of radio devices. There are many advantages of migrating into software, including better functionality, lower manufacturing costs, smaller device dimensions together with lower power consumption, and usually greater quality, since DSP algorithms are not subject to parasitic effects in the way the hardware parts are. But there are still more advantages. The software allows for flexibility and reconfiguration [2].

By using SDR Technique a family of Radio products used in communication to be developed in common platform architecture and lot of research work is going on in this area allowing new products will come quickly into market. Since the software to be reused across radio products, the development cost reduces dramatically. This type of wireless communication enables the user to communicate with whomever they need to communicate and in whatever manner according to their wish. For example video call is available in Third generation. Likewise any type of applications can be include using SDR in a single chip. The main advantage SDR engineers is to provide a single radio transceiver capable of playing the roles of cordless telephone, cell phone(GSM and CDMA),

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 11, November 2013

#### **II.ARCHITECTURE**

By using SDR Technique a family of Radio products used in communication to be developed in common platform architecture and lot of research work is going on in this area allowing new products will come quickly into market. Since the software to be reused across radio products, the development cost reduces dramatically. This type of wireless communication enables the user to communicate with whomever they need to communicate and in whatever manner according to their wish. For example video call is available in Third generation. Likewise any type of applications can be include using SDR in a single chip[10][11].

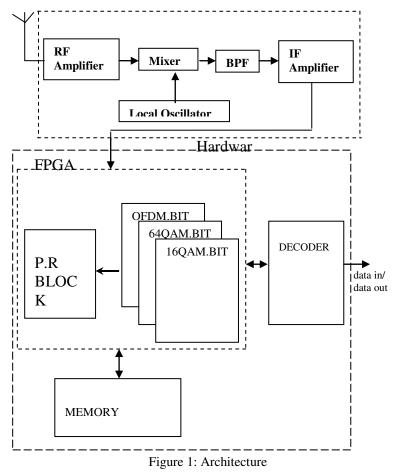

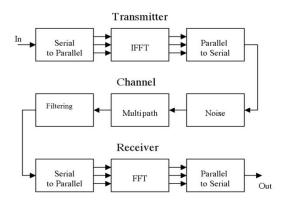

As shown in the block diagram, we have proposed a SDR architecture with only FPGA due to the availability of massive parallelism and Partial Reconfigurable ability. Since the newer FPGA provides PR modules, it is possible to change of the certain part of FPGA alone and hence we can avoid complete FPGA for reconfiguration. The embedded PowerPC and DSP slices can do a work of a GPP or DSP. Hence it is also not required to use dedicated

In most cases DSP is used because the combination of controlling ability and signal processing power. The different demodulation techniques configuration will be loaded into a memory unit initially.

Orthogonal frequency-division multiplexing (OFDM) is the modulation technique for European standards such as the Digital Audio Broadcasting (DAB) and the Digital Video Broadcasting (DVB) systems. As such it has received much attention and has been proposed for many other applications, OFDM is a type of multichannel modulation that divides a given channel into many parallel sub-channels or subcarriers, so that multiple symbols are sent in parallel. The order (M) of the entire OFDM signal is the sum of the orders of each subcarrier, representing the total number of

states available to the OFDM signal. For OFDM with N subcarriers we have

$M_{OFDM} = N. N_{QAM}$

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 11, November 2013

### **III. RE-CONFIGURABILITY**

The static logic remains functioning and is completely unaffected by the loading of a partial bit file. The reconfigurable logic is replaced by the contents of the partial bit file. There will be a Configuration controller which is part of the static module. This takes care of loading and unloading of dynamic modules. The command to this controller will be given from PowerPC with the reconfiguration data[8][9].

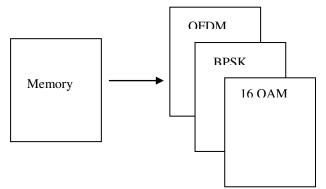

Figure2: Partial Reconfiguration

The above diagram shows the BIT files in partial reconfigurable (PR) block in FPGA. The BIT files can be stored in this as OFDM.BIT, QAM.BIT and BPSK.BIT. The Bit files can be select according the SNR value.

#### IV. OFDMA

Orthogonal frequency-division multiplexing (OFDM) is a transmission technique that modulates multiple carriers simultaneously. Although their spectra overlap, the transmitted multiple carriers can be demodulated orthogonally, provided that correct time windowing is used at the receiver. Since the OFDM-based system has high spectral efficiency and is robust against intersymbol interference and frequency-selective fading channels, it has been widely chosen for European digital audio/video broadcasting and wireless local/ metropolitan area network standards, and now, it is used in most broadband wireless communication systems[4].

In OFDM the modulation used on each subcarrier is QAM, and there is no filtering used on the individual subcarriers. For each OFDM symbol the data is distributed among the subcarriers: 2 bits each when 4-QAM is used; 6 bits each if 64 QAM is used. The OFDM time waveform is the sum of the magnitude and phase scaled subcarrier sinusoids at each frequency used. Since all subcarriers use the same symbol time, the OFDM waveform also has this symbol time.

One of the severe drawbacks with OFDM systems, however, is the high peak-to-average power ratio (PAPR) of transmitted signals. The high PAPR introduces inter-modulation distortion and undesired out-of-band radiation due to the nonlinearity of the high power amplifier (HPA). The distortion and radiation cause degradation of the bit error rate (BER) and high adjacent channel interference, respectively. Therefore, it is desirable to reduce the PAPR of an OFDM signal[12].

The PAPR is given by the equation

$PAPR = \frac{P_{peak}}{P_{average}}$ Where, P<sub>peak</sub> is the Peak power of the OFDM signal and P<sub>average</sub> is the average power.

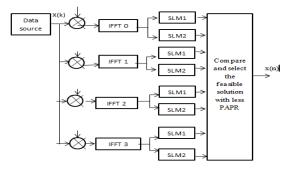

The FFT of the can be calculated by using Decimation in Time, Radix 2 algorithm. Then using two SLM we can select the Signal with minimum PAPR in each FFT samples.

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 11, November 2013

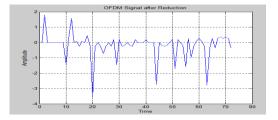

The above system the information signal from the receiver X(k) is divided into four equal parts as  $X_1(k)$ ,  $X_2(k)$ .  $X_3(k)$ .  $X_3(k)$ . after the division the two ifft will be calculated and find out the PAPR ratio. Finally select the signal with less PAPR ratio in the receiver  $x_1(n)$ ,  $x_2(n)$ ,  $x_3(n)$ ,  $x_4(n)$  and combined the four ifft will get the signal x(n).

$$PAPR = \frac{\max_{0 \le t \le T} |x(t)|^2}{\sigma^2}$$

Where, x(t) is the input signal from the Centre.

After finding the FFT it can be denoted as x(n). The FFT can be scalable, N can be 64, 128, 256, 512, 1024 and 2048. Any filtering used to smooth out these waveform discontinuities necessarily distorts each OFDM symbol waveform. And since the OFDM waveform is generated solely from the data on each subcarrier, any filtering distortion increases EVM. OFDM is not nearly as tolerant of EVM as filtered QAM signals are, as noted from comparing their respective EVM specification limits: 3% for OFDM, 10% or more for QAM[13].

Figure4: OFDM System Architecture

The modulation used in this are BPSK and 16-QAM. The number of inputs is divided into four. Here Four IFFTs are used to reduce the PAPR. But by division the speed will be reduced. This can be rectified by using parallel processing. Cyclic prefix acts as a buffer region where delayed information from the previous symbols can get stored. The receiver has to exclude samples from the cyclic prefix which got corrupted by the previous symbol when choosing the samples for an OFDM symbol. Typically, cyclic prefix duration is determined by the expected duration of the multipath channel in the operating environment.

$\begin{aligned} \mathbf{x}(\mathbf{n}) &= \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} \mathbf{X}(\mathbf{k}) e^{j2\pi nk/N} \\ \text{Where, } \mathbf{n} &= 0, 1, 2 \dots \dots N-1. \\ \mathbf{x}(\mathbf{n}) \text{ is the information signal.} \\ \text{N is the number of samples.} \end{aligned}$

Copyright to IJAREEIE

www.ijareeie.com

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 11, November 2013

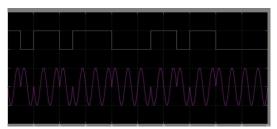

BPSK : BPSK is the simplest form of phase shift keying (PSK). It uses two phases which are separated by  $180^{\circ}$  and so can also be termed 2-PSK. It does not particularly matter exactly where the constellation points are positioned, and in this figure they are shown on the real axis, at  $0^{\circ}$  and  $180^{\circ}$ .

$$s_n(t) = \sqrt{\frac{2E_b}{T_b}}\cos(2\pi f_c t + \pi(1-n)), n = 0, 1.$$

Where s(t) is the modulated signal.

QAM:- 16 QAM : 16-state quadrature amplitude modulation have four I values and four Q values yielding four bits per symbol. It has 16 states because  $2^4 = 16$ . The theoretical bandwidth efficiency is 4 bits/ second/Hz. Data is split into two channels, I and Q, each channel can take on two phases. The in phase and quadrature can vary separately. However, 16-QAM can accommodate two intermediate amplitude values. Two bits are routed to each channel simultaneously. The two bits for each channel are added, then applied to the respective channel modulator.

$$S_{m}(t) = \sum_{m} (A_{m}e^{i\theta_{m}})g(t - mT)e^{i2\pi f_{c}t}$$

$$= A_{m}g(t)[\cos(2\pi f_{c}t + \theta_{m}) + \sin(2\pi f_{c}t + \theta_{m})$$

Where,  $A_{m} = (A_{I}^{2} + A_{Q}^{2})^{1/2}$ .

$$A_{I}, A_{Q} \longrightarrow \text{ amplitudes of Information signal and Quadrature carriers.}$$

$$g(t) \longrightarrow \text{ the signal pulse}$$

$$\theta_{m} \longrightarrow \text{ indicates phase modulation has value}$$

$$\theta_{m} = \tan^{-1}\frac{A_{Q}}{A_{I}}$$

The state of the QAM are scalable in nature. So the state can selected according to the application and the feature size. The state can be 4, 16, 32,64, and 128. If you recall, in the post on BER computation in AWGN, the probability of error for transmission of either +1 or -1 is computed by integrating the tail of the Gaussian probability density function for a given value of bit energy to noise ratio  $E_b/N_o$ . The theoretical bit error rate for BPSK modulation

$$P_{b,BPSK} = \frac{1}{2} erfc \left( \sqrt{\frac{E_b}{N_0}} \right)$$

According to the bit error rate we can select the modulation. If the system is transmitted with high bit error rate receiver send a feedback signal to change the modulation type and resend the message again.

#### **IV. RESULTS**

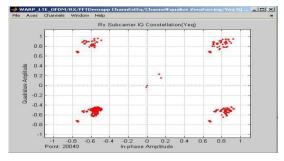

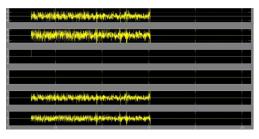

The Simulation is done by using Xilinx system generator and Matlab. The Synthesis is done by using Xilinx ISE Software. The Simulation results are shown in the figures. The Modulation can be selected at the receiver according to the features. This features are extracted by adding white noise to the channel.

Figure 5: Constellation

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 11, November 2013

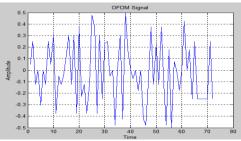

Figure 6: OFDM Signal with 64QAM

Figure 7: BPSK modulation

Figure 8: OFDM signal with QPSK

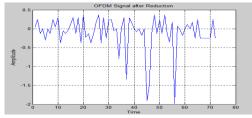

Figure 9: OFDM signal after power reduction

Figure 10: OFDM signal with BPSK

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 2, Issue 11, November 2013

#### V. CONCLUSION

Realization of SDR Developed by using Xilinx FPGA. Due to the Realization is done by using the help of run time Reconfiguration, the flexibility and performance can be improved. The area also can be decreased. The New Xilinx, Vertex Series FPGA provides the provision of Partial Reconfiguration. The PAPR can be reduced by using Partial transmit sequence.

This SDR Receiver can be used for military application and 4G wireless communication. The use of run time reconfiguration helps to change the coding according to the application. For future work the optimization algorithms like Genetic algorithm can be used for are and power minimization.

#### REFERENCES

- [1]. Neenu Joseph, Dr. P Nirmal kumar, Anna university:-" Power consumption reduction in a SDR based wireless communication system using partial reconfigurable FPGA":-, VLSICS-2012

- [2]. P. Pawłowski, A. Dąbrowski, P. Skrzypek, P. Roszak, A. Pałejko, T. Walenciak, M. Mor:-"Software Defined Radio Design and implementation of complete platform", IEEE, 2011

- [3]. Zhongjun Zhao, Yongliang Shen, Yuan Bai,:-"Design and Implementation of the BPSK Modem Based on Software Defined Radio", International Conference on Instrumentation, Measurment, computer, communication and control, 2011

- [4]. Chang Eon Shin, Kyung Soo Rim, and Youngok Kim :-"A Weighted OFDM Signal Scheme for Peak-to-Average Power Ratio Reduction of OFDM Signals", IEEE Transactions on Vehicular Technology, Vol. 62, No. 3, pp 1406-1410, March2013

- [5]. H. Yoshida, H. Tsurumi, and Y. Suzuki, "Broadband RF front-end and software execution procedure in software defined radio," in Proc. IEEE Veh. Technol. Conference., vol. 4, pp. 2133–2137, 1999.

- [6]. F. Rivet, Y. Deval, J. B. Begueret, D. Dallet, and D. Belot, "A disruptive software-defined radio receiver architecture based on sampled analog signal processing," in Proc. IEEE Radio Frequency Integr. Circuits (RFIC) Symp., pp. 197–200, Jun. 3–5, 2007,.

- [7]. A. Abidi, "The path to the software-defined radio receiver," IEEE J. Solid-State Circ., vol. 42, no. 5, pp. 954–966, May 2007

- [8]. FPGA Run-Time Reconfiguration: Two Approaches: www. Altera.com

- [9]. Partial Reconfiguration of Virtex FPGAs in ISE 12:- www.xlinx.com

- [10]. J Glossner, D Inacu, J Lu, E Hokenek and M Moudgill :- "A Software Defined Communications baseband design," IEEE Communication Mag vol. 41, no.1, pp. 120–128, Jan. 2003.

- [11]. L. Zhigang, L wei, Z.Yan and G Wei," Multi standard SDR base band platform," in Proc. IEEE Int. Conf. Computer Networks and Mobile Computing. pp. 461–464, 2003.

- [12]. Chin-Liang Wang, Sheng-Ju Ku, and Chun-Ju Yang:- "A Low-Complexity PAPR Estimation Scheme for OFDM Signals and Its Application to SLM-Based PAPR Reduction" IEEE Journal of selected topics in signal processing, vol 4, no.3, pp 637 – 646, June 2010

- [13]. Tao Jiang, Chunxing Ni, and Lili Guan :- A Novel Phase Offset SLM Scheme for PAPR Reduction in Alamouti MIMO-OFDM Systems Without Side Information, IEEE signal processing letters, vol. 20, no. 4, april 2013.

#### BIOGRAPHY

Neenu Joseph: Finished B.Tech from Cochin University in Electronics and Communication. completed M.E in VLSI From Anna University. Now doing P.hD In Anna University in SDR application in Reconfigurable FPGA.

<sup>2</sup> Dr. P Nirmal Kumar: Finished B.Tech from Madras University in Electrical and Electronics. Completed M.E in Applied Electronics from Anna University. Finished P.hD In Anna University in Evolvable Hardware and now working as Associate Professor in Anna University.