An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

# Voltage Balancing Control of Improved ZVS FBTL Converter for WECS

# Janani.K<sup>1</sup>, Anbarasu.L<sup>2</sup>

PG Scholar, Erode Sengunthar Engineering College, Thudupathi, Erode, Tamilnadu, India<sup>1</sup> Assistant Professor, Erode Sengunthar Engineering College, Thudupathi, Erode, Tamilnadu, India<sup>2</sup>

Abstract— This project proposes a newly developed three level dc-dc converter which is designed with zero voltage switching technique for the purpose of reducing conduction loss and frequent switching of the switches used in the converter. A passive filter is used to reduce the primary voltage stress of medium frequency transformer and to improve the performance of the converter. A modulation strategy, including two operation modes, is proposed for the IFBTL dc/dc converter. Furthermore a voltage balancing control strategy is also proposed for the improved ZVS full bridge three level DC-DC converter. With the passive filter and the modulation strategy, the voltage stress of the transformer in the Improved ZVS FBTL DC/DC converter can be effectively reduced, which is very significant in the medium-voltage and high-power application. It is performed by designing a full bridge three level converter with ZVS technique and a passive filter and the converter is simulated using MATLAB SIMULINK.

Keywords— ZVS, Passive filter, MFT, FBTL converter, WECS

## I. INTRODUCTION

Power converters play a vital role in the integration of wind power into the electrical grid. Multilevel converters can obtain high voltage level with low cost, easy available of low-voltage devices which reduces the size and cost of the filters and increases the performance of the converter due to the characteristics of the staircase shaped outputs. And also the convenient way of reducing the voltage stress of the converter is by using the multilevel technology which is good one for high voltage and high frequency applications. When the full bridge two level and half bridge three level converters are been considered, the voltage change rate, dv/dt is high which may cause large electromagnetic interference. And also the number of switches used is more; voltage sensors are been

required for few converter types. The offshore wind turbines may be directly connected into a DC grid to deliver dc power to a medium- or high-DC voltage network.

Normally, the voltage level of the dc network would be dozens of kilovolts which is much higher than the input voltage of the dc-dc converter. Hence, a medium frequency transformer (MFT) operated at hundreds of hertz to several kilohertz would be installed in the dc/dc converter, which not only ensures that the input voltage can be boosted to a desired high output voltage, but also achieves the galvanic isolation between source and grid. Besides, owing to the high-voltage level in the dc network, the usage of the diode bridges in the dc/dc converters could be advantageous.

Moreover the voltage balancing control is not possible for two level converters and complicated for sub module based one. Hence full bridge three level converters have a simpler circuit structure and less number of switching devices. In order to reduce the voltage stress and the switching losses in the device, an improved ZVS (Zero Voltage Switching) full bridge three level DC-DC converter is proposed. The converter is capable of achieving zero voltage switching for all the power switches and the voltage stress is also reduced. Zero Voltage Switching means that the power to the load is switched on or off only when the output voltage is zero volts. Zero Voltage Switching can extend the life of a controller and of the load being controlled.

Varying from other converter design a passive filter is introduced which improves the performance of the converter. The alternating voltage which is obtained from the inverter is fed through the passive filter which reduces the stress and can effectively overcome the problems which occurs due to the non linear characteristics of the semiconductor devices which results in the distorted waveforms. This voltage is fed to the medium frequency transformer (MFT) which in turn steps up the voltage and is been fed to the converter which is essential for a power

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

## International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

converter in high power applications. FBTL converter has simple circuit structure and less number of switching devices with improved dynamic response. In this project, an improved ZVS FBTL DC-DC converter is proposed with a voltage balancing control strategy.

## II. PAGE LAYOUT

DC-DC converters comprising of an inverter system to invert the DC input voltage with IGBT switches and a transformer to step up the inverted AC voltage and a rectifier system to convert the inverted voltage is used in the wind energy conversion system.

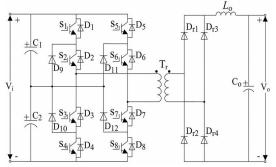

Fig 1 Full Bridge Three Level DC-DC Converter

Fig 1 shows the circuit diagram for Full Bridge Three Level DC-DC Converter. The circuit comprises of the foresaid inverter system to invert the DC input voltage, a transformer which helps to step up the inverted AC voltage. Stepped up AC voltage is then fed to the rectifier system and converted as DC voltage. Though the converter comprises of less number of switches, conduction loss is high and also voltage stress is present in the inverted voltage. Considering these two factors Improved ZVS FBTL Converter is designed which ZVS technique for switching operation which reduces the conduction loss and a passive filter is used to reduce the voltage stress of the inverted voltage.

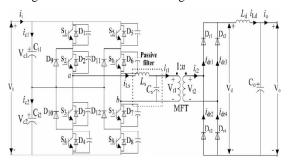

Fig 2 Circuit Diagram For Improved ZVS Full Bridge Three Level Dc-Dc Converter

Fig 2 shows the circuit diagram for Improved ZVS FBTL converter where the circuit is composed of eight switches  $(S_1-S_8)$ , eight freewheeling diodes  $(D_1-D_8)$ , four clamping diodes (D9-D12), an MFT, four rectifier diodes  $(D_{r1}-D_{r4})$ , a passive filter (L<sub>s</sub> and C<sub>s</sub>), an output filter inductor  $L_d$  , an output capacitor  $C_{\rm o}$  ,and two voltage divided capacitors ( $C_{i1}$  and  $C_{i2}$  ), which are used to split the dc bus voltage V<sub>i</sub> into two equal voltages V<sub>c1</sub>and  $V_{c2}$  .Different from the FBTL dc/dc converter, zero voltage switching is been employed across the switches in the converter to reduce the switching losses and a passive filter is inserted into the IFBTL dc/dc converter to improve the performance of the dc/dc converter, which can effectively overcome the problem that the nonlinear characteristics of semiconductor devices result in distorted waveforms associated with harmonics and reduce the voltage stress of the MFT, which is very significant for the power converter in the high-power application.

## A. Proposed Modulation Strategy

The switches S1–S8 are switched complementarily in pairs with a pulse width modulation (PWM), i.e., pairs S<sub>1</sub>–S<sub>3</sub>, S4–S<sub>2</sub>, S5–S<sub>7</sub>, and S<sub>8</sub>–S<sub>6</sub>, respectively. The duty cycle for S<sub>1</sub> is D. The way of phase shifting the PWM for other switch pairs results in the different operation modes as follows.

1) Operation Mode I: The PWM waveform for the pairs  $S_8 - S_6, \, S_5 - S_7, \, and \, S_4 - S_2$  lags behind that for pair  $S_{1^-} S_3 \, by(D - D_c )Ts \, /2, \, Ts \, /2, \, and \, (D - Dc + 1)Ts \, /2$  respectively and  $T_s$  is the switching cycle. The overlap time between  $S_1 - S_3$  and  $S_8 - S_6$  is DC Ts /2, which is also for  $S_4 - S_2$  and  $S_5 - S_7$ .  $D_C$  is defined as the overlap duty ratio.

2) Operation Mode II: The PWM waveform for pair  $S_8$ - $S_6$  leads before that for pair  $S_1$ - $S_3$  by  $(D - D_c)T_s$  /2, and the PWM waveform for pairs  $S_4$ - $S_2$  and  $S_5$ - $S_7$  lags behind that for the pair  $S_1$ - $S_3$  by  $(1 - D + D_c)T_s$  /2and  $T_s$  /2, respectively. The overlap time between  $S_1$ - $S_3$  and  $S_8$ - $S_6$  and between  $S_4$ - $S_2$  and  $S_5$ - $S_7$  is also both  $D_C$  Ts /2.

The main difference between the two operation modes is the capacitor charge and discharge situations in each half cycle. In operation mode I, capacitor  $C_{i2}$  discharges more energy than capacitor  $C_{i1}$  in each half cycle while capacitors  $C_{i1}$  and the  $C_{i2}$  exchange their situations in operation mode II. In operation mode II, capacitor  $C_{i1}$  discharges more energy than capacitor  $C_{i2}$  in each half cycle. The two operation modes can be

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

alternatively used for the adaptive voltage balancing control.

The steady-state operations of the converter under the proposed modulation strategy are explained with the assumption that  $C_{i1} = C_{i2}$  Voltages  $V_{ab}$ ,  $V_{t1}$ ,  $V_{t2}$  and currents  $i_{Ls}$ ,  $i_{t1}$ ,  $i_{t2}$  are all periodic waveforms with period  $T_s$ . Currents  $i_{c1}$ ,  $i_{c2}$ , and  $i_{Ld}$  are with the period Ts /2.Owing to the passive filter in the IFBTL dc/dc converter, the performance of voltages  $V_{t1}$ ,  $V_{t2}$  and currents  $i_{t1}$ ,  $i_{t2}$  associated with the MFT is effectively improved, which is significant for the IFBTL dc/dc converter in the applications of the medium-voltage and high-power system.

#### III. COMPARISON BETWEEN BASIC FBTL AND IMPROVED ZVS FBTL CONVERTER

The need of ZVS operation and passive filters for the converters used in wind energy conversion system can be brought down by comparing a FBTL converter and an Improved ZVS FBTL converter. Simulation is carried out with the following parameters for the converter for input voltage rating of 250V. Both the converters have same parameters and IGBT switches are used. The only difference between the converters is that in the Improved ZVS FBTL converter passive filter and ZVS technique are been used and the experiment is carried using simulation.

TABLE ICONVERTER PARAMETERS

| S.No | Parameter                           | Value |

|------|-------------------------------------|-------|

| 1    | Capacitors $C_{i1}$ , $C_{i2}$ (µf) | 330   |

| 2    | Inductance, L <sub>s</sub> (mh)     | 0.4   |

| 3    | Capacitance, $C_s$ (µf)             | 3     |

| 4    | Turn Ratio of MFT                   | 1:2.6 |

| 5    | Inductance, L <sub>d</sub> (mh)     | 0.4   |

| 6    | Capacitance, $C_o$ (µf)             | 1000  |

| 7    | DC network voltage, $V_o(v)$        | 250   |

| 8    | DC network inductance (mh)          | 0.4   |

| 9    | DC network resistance( $\Omega$ )   | 1     |

For experimental purpose an input voltage of 250V ideal DC voltage is been fed to the FBTL converter which

is composed of eight switches (S<sub>1</sub>–S<sub>8</sub>), eight freewheeling diodes (D<sub>1</sub>–D<sub>8</sub>), four clamping diodes (D<sub>9</sub>–D<sub>12</sub>),an MFT, four rectifier diodes (D<sub>r1</sub>–D<sub>r4</sub>), an output filter inductor L<sub>d</sub>, an output capacitor C<sub>o</sub>, and two voltage divided capacitors (C<sub>i1</sub> and C<sub>i2</sub>), which are used to split the dc bus voltage V<sub>i</sub> into two equal voltages V<sub>c1</sub> and V<sub>c2</sub>. The working of this converter is normal to that of a power converter where the input ideal DC voltage is converted into alternating voltage and fed into a medium frequency transformer.

Due to the switching operation, the losses due to switching reduce the efficiency of the alternating voltage and the voltage stress will also be high. The alternating voltage is then fed to the medium frequency transformer which steps up the input voltage with the presence of voltage stress. The stepped up alternating voltage is fed to a diode converter which converts the alternating voltage to DC voltage.

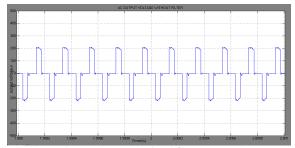

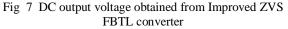

Fig 3 Alternating Voltage Obtained from FBTL Converter Fig 3 shows the output waveform obtained from the inverter when a 250V DC input voltage is fed to it. The switches conduct providing two operation modes as mentioned above and due to the conduction of the switches losses occur. And also the stress in the voltage is been produced. For a 250V input DC voltage the inverted output from a FBTL converter is about 200V. This is only due to the conduction loss and voltage stress.

Obtained alternating voltage is fed to a medium frequency transformer which steps up the fed alternating

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

# Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

voltage and is been converted into DC voltage with the help of diode rectifier.

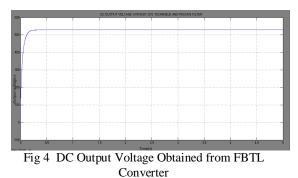

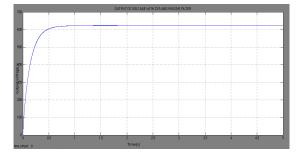

For the given input of 250V, after boosting up the voltage the output DC voltage obtained from a FBTL converter is about 530V. To overcome the switching losses Zero Voltage Switching technique has to be implemented.

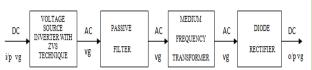

## Fig 5 Block Diagram for Proposed System

For the voltage supply of 250V DC voltage, obtained alternating voltage from the converter is about 200V and the above figure clearly shows that the obtained waveform contains no voltage stress and the waveform is accurately sinusoidal. This is due to the reason that, when

Obtained alternating voltage is fed to a medium frequency transformer which steps up the fed alternating voltage and is been converted into DC voltage with the help of diode rectifier.

For the given input of 250V, after boosting up the voltage the output DC voltage obtained from Improved ZVS FBTL converter is about 620V. The switching losses are been eliminated by implementing ZVS technique and the voltage stress is reduced by using passive filter. The output voltage obtained is much higher than the output obtained from a FBTL converter with a big difference of about 100V.

Obtained DC output voltage shows a major difference from the normal FBTL converter where the difference between the voltages is about 100V. This is due to reason that the performance of the converter is improved by using passive filter which eliminates the voltage stress of

the DC voltage is supplied to the converter it gets split

when passing through the capacitors and the voltage

passes through the switches. Due to the switching

operation, with zero voltage switching, the losses are been

Fig 6 Alternating Voltage Obtained from Improved ZVS FBTL Converter

the primary voltage fed to the Medium Frequency Transformer. Moreover the switching operation is carried out using ZVS technique which reduces the switching losses and hence therefore the output is efficient.

## IV. VOLTAGE BALANCING CONTROL STRATEGY

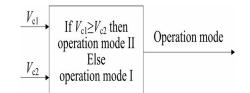

A voltage balancing control strategy is proposed for the Improved ZVS FBTL dc/dc converter in this section, which can be realized by alternating the operation modes I and II.

Fig 8 Block diagram of the proposed voltage balancing control for Improved ZVS FBTL converter

I) Operation Mode I: Here both the capacitor currents  $i_{c1}$  and  $i_{c2}$  are with the period of Ts /2. In the first half cycle, the charge or discharge situations for capacitors  $C_{i1}$  and  $C_{i2}$  in stages A, C, and E are the same. In stage B, current  $i_{c2}$  is more than  $i_{c1}$ , while  $i_{c2}$  is far less than  $i_{c1}$  in stage D. Owing to that, of stages B and D are (D – Dc) Ts /2. Suppose  $V_{c1} = V_{c2} = V_i /2$ ;  $C_{i2}$  would provide more energy to the load than  $C_{i1}$  in the first half cycle under the operation mode I. The situation in the second half cycle is similar to that in the first half

An ISO 3297: 2007 Certified Organization,

Volume 3, Special Issue 1, February 2014

International Conference on Engineering Technology and Science-(ICETS'14)

On 10<sup>th</sup> & 11<sup>th</sup> February Organized by

#### Department of CIVIL, CSE, ECE, EEE, MECHNICAL Engg. and S&H of Muthayammal College of Engineering, Rasipuram, Tamilnadu, India

cycle. Consequently, voltage  $V_{c1}$  would be increased and voltage  $V_{c2}$  would be reduced in operation mode I, which would result in the trend that voltage  $V_{c1}$  would be more than  $V_{c2}$  in operation mode I. operation mode I is selected in the next half cycle when  $V_{c1}$  is less than  $V_{c2}\!.$

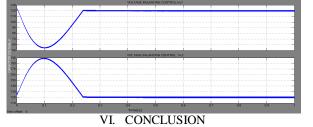

Fig 10 Balanced capacitor voltages

2) Operation Mode II: The same to operation mode I, the charge and discharge situations for capacitors  $C_{i1}$  and  $C_{i2}$  in stages A, C, and E are the same as in the first half cycle. The only difference is that current  $i_{c2}$  is less than  $i_{c1}$  in stage D, while  $i_{c2}$  is far more than  $i_{c1}$  in stage B in operation mode II, which is contrary to that in operation mode I. The periods for stages B and D are both (D – Dc) Ts /2. Suppose  $V_{c1} = V_{c2} = V_i /2$ ;  $C_{i1}$  would provide more energy to the load than  $C_{i2}$  in the first half cycle under the operation mode II. The situation in the second half cycle is similar to the first half cycle. Therefore, voltage  $V_{c1}$  would be reduced and voltage  $V_{c2}$  would be increased in operation mode II, which would result in the trend that voltage  $V_{c1}$  would be less than  $V_{c2}$  in operation mode II.

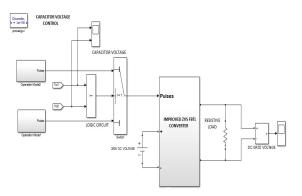

## V. SIMULATION CIRCUIT

The simulation circuit for voltage balancing control of the capacitor is shown in the Fig 9 where the voltage balancing control block is attached to the designed Improved ZVS FBTL Converter.

## Fig 9 Simulation Circuit for Voltage Balancing Control of Improved ZVS FBTL Converter

#### VI. RESULT OBTAINED FROM VOLTAGE BALANCING CONTROL CIRCUIT

Based on the aforesaid analysis,  $V_{c1}$  would be more than  $V_{c2}$  in operation mode I, and  $V_{c1}$  would be less than  $V_{c2}$  in operation mode II. Consequently, a control strategy is proposed for the capacitor voltage balancing where a comparator is used here with two input voltages  $V_{c1}$  and  $V_{c2}$ . If  $V_{c1}$  is more than  $V_{c2}$ , the operation mode in the next half cycle is selected as II. On the contrary, the

This paper has presented the control of the Improved ZVS FBTL dc/dc converter for the wind turbine system to facilitate the integration of wind turbines into a dc grid. The corresponding modulation strategy, including operation modes I and II, are proposed for the Improved ZVS FBTL dc/dc converter. The proposed two operation modes are discussed in detail. A voltage balancing control strategy is proposed for the Improved ZVS FBTL dc/dc converter, where the alternation of the proposed two operation modes can keep the capacitor voltage balanced. With the passive filter and the modulation strategy, the voltage stress of the transformer in the Improved ZVS FBTL dc/dc converter can be effectively reduced, which is very significant in the medium-voltage and high-power application and ZVS technique has reduced the switching losses in the switch. The converter is designed and simulated using MATLAB SIMULINK.

#### REFERENCES

$[1]\,$  J. Robinson, D. Jovcic, and G. Jo'os, "Analysis and design of an offshore wind farm using a MV DC grid," IEEE Trans. Power Delivery, vol. 25 no. 4, pp. 2164–2173, Oct 2010.

[2] F. Blaabjerg, Z. Chen, and B.S.Kjaer, "Power electronics as efficient interface in dispersed power generation systems," IEEE Trans. Power Electron., vol. 19, no. 5, pp 1184–1194, Sep. 2004.

[3] N. Y. Dai, M. C.Wong, and Y. D. Han, "Application of a threelevel NPC inverter as a three -phase fourwire power quality compensator by generalized 3DSVM," IEEE Trans. Power Electron., vol. 21, no. 2, pp 440–449, Mar. 2006.

[4] X. Ruan, B. Li, Q. Chen, S. C. Tan, and C. K. Tse, "Fundamental considerations of three level dc-dc converters: Topologies, analyses, and control,"IEEE Trans. Circuits Syst. I, Reg. Paers, vol. 55, no. 11, pp. 3733–3743.Dec. 2008.

[5] Z. Zhang and X. Ruan, "ZVS PWM full-bridge three-level converter,"in Proc. 4th Int. Power Electron. Motion Control Conf., 2004, pp. 1085–1090.

[6] P. M. Barbosa, F. Canales, J. M. Burd'10, and F. C. Lee, "A threelevel converter and its application to power factor correction," IEEE Trans. Power Electron., vol. 20, no. 6, pp. 1319–1327, Nov. 2005.

[7] J. R. Pinheiro and I. Barbi, "The three-level ZVS -PWM dcto-dc converter," IEEE Trans. Power Electron., vol. 8, no. 4, pp. 486–492, Oct. 1993.